- 您現在的位置:買賣IC網 > PDF目錄372150 > SMX320C6203W14 (Texas Instruments, Inc.) FLOATING-POINT DIGITAL SIGNAL PROCESSOR PDF資料下載

參數資料

| 型號: | SMX320C6203W14 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 浮點數字信號處理器 |

| 文件頁數: | 42/64頁 |

| 文件大小: | 939K |

| 代理商: | SMX320C6203W14 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

SGUS030B

–

APRIL 2000

–

REVISED MAY 2001

42

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

–

1443

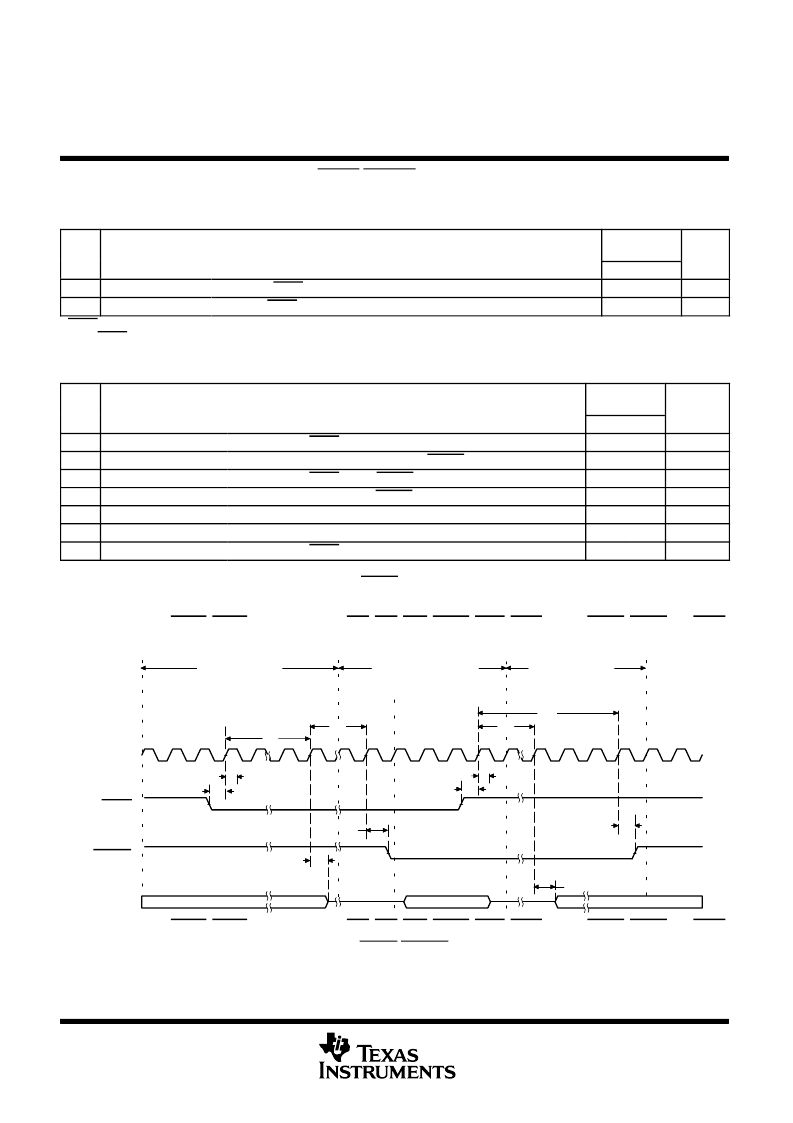

HOLD/HOLDA TIMING

timing requirements for the hold/hold acknowledge cycles

(see Figure 24)

NO.

’

C6701-14

’

C6701-16

UNIT

MIN

MAX

1

tsu(HOLDH-CKO1H)

th(CKO1H-HOLDL)

HOLD is synchronized internally. Therefore, if setup and hold times are not met, it will either be recognized in the current cycle or in the next cycle.

Thus, HOLD can be an asynchronous input.

Setup time, HOLD high before CLKOUT1 high

5

ns

2

Hold time, HOLD low after CLKOUT1 high

2

ns

switching characteristics for the hold/hold acknowledge cycles

(see Figure 24)

NO.

PARAMETER

’

C6701-14

’

C6701-16

UNIT

MIN

MAX

3

tR(HOLDL-EMHZ)

tR(EMHZ-HOLDAL)

tR(HOLDH-HOLDAH)

td(CKO1H-HOLDAL)

td(CKO1H-BHZ)

td(CKO1H-BLZ)

tR(HOLDH-BLZ)

P = 1/CPU clock frequency in ns. For example, when running parts at 167 MHz, use P = 6 ns.

§

All pending EMIF transactions are allowed to complete before HOLDA is asserted. The worst cases for this is an asynchronous read or write

with external ARDY used or a minimum of eight consecutive SDRAM reads or writes when RBTR8 = 1. If no bus transactions are occurring, then

the minimum delay time can be achieved. Also, bus hold can be indefinitely delayed by setting the NOHOLD = 1.

EMIF Bus consists of CE[3:0], BE[3:0], ED[31:0], EA[21:2], ARE, AOE, AWE, SSADS, SSOE, SSWE, SDA10, SDRAS, SDCAS, and SDWE.

*This parameter is not tested.

Response time, HOLD low to EMIF high impedance

4P

§

ns

4

Response time, EMIF high impedance to HOLDA low

2P

ns

5

Response time, HOLD high to HOLDA high

4P

7P

ns

6

Delay time, CLKOUT1 high to HOLDA valid

Delay time, CLKOUT1 high to EMIF Bus high impedance

Delay time, CLKOUT1 high to EMIF Bus low impedance

Response time, HOLD high to EMIF Bus low impedance

1

8

ns

7

*1

*8

ns

8

*1

*12

ns

9

3P

6P

ns

DSP Owns Bus

External Requester

DSP Owns Bus

’

C6701

Ext Req

’

C6701

8

7

3

4

6

6

1

2

CLKOUT1

HOLD

HOLDA

EMIF Bus

1

5

9

2

EMIF Bus consists of CE[3:0], BE[3:0], ED[31:0], EA[21:2], ARE, AOE, AWE, SSADS, SSOE, SSWE, SDA10, SDRAS, SDCAS, and SDWE.

Figure 24. HOLD/HOLDA Timing

相關PDF資料 |

PDF描述 |

|---|---|

| SMX320C6203W16 | FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM4A | Double-Balanced Mixer |

| SM4B | Double-Balanced Mixer |

| SM4G | Double-Balanced Mixer |

| SM4T17 | Load Insensitive Mixer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SMX320C6203W16 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SMX320C6413GTS400 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processors |

| SMX320C6413GTS500 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processors |

| SMX320C6413GTSA400 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processors |

| SMX320C6413GTSA500 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processors |

發(fā)布緊急采購,3分鐘左右您將得到回復。