- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378698 > SM5902AF (Seiko NPC Corporation) compression and non compression type shock-proof memory controller PDF資料下載

參數(shù)資料

| 型號(hào): | SM5902AF |

| 廠商: | Seiko NPC Corporation |

| 英文描述: | compression and non compression type shock-proof memory controller |

| 中文描述: | 壓縮和非壓縮式防震內(nèi)存控制器 |

| 文件頁數(shù): | 22/40頁 |

| 文件大?。?/td> | 312K |

| 代理商: | SM5902AF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

86H (digital audio interface settings)

- CP1, CP2 (channel status and clock accuracy set-

ting)

When 0 and 0: Level 2 (max ± 300 ppm)

When 0 and 1: Level 3I (max ± 10%)

When 1 and 0: Level 1 (max ± 50 ppm)

When 1 and 1: Not supported

- LBIT (digital audio signal generation logic)

When 1: Not assigned

When 0: Post-recording software

- DIT (digital audio interface enable)

When 1: DIT output enable

When 0: DIT LOW-level output

87H (subcode Q data setting)

- QAD3 to QAD0 (Q data setting and word address

specification)

QAD3 (MSB) to QAD0 (LSB) specify one of 10

valid addresses in the range 0000 to 1001.

If an address in the range 1010 to 1111 is speci-

fied, the data on QD7 to QD0 is ignored.

Note that writing to address 1001 also functions

as the write stop command.

- QD7 to QD0 (Q data setting and word data)

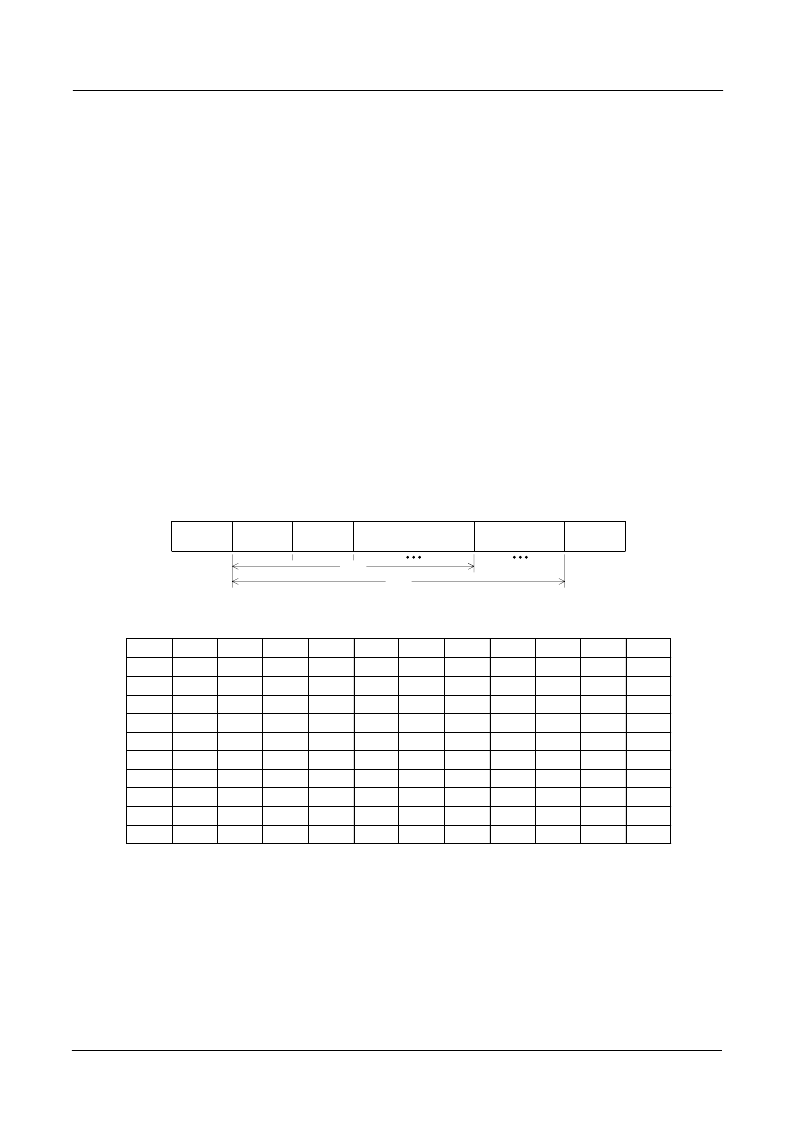

The CD Q-channel has the general data format

shown below.

The write data required to fully specify the Q data

is the 80 bits comprising CONTROL, ADR, and

DATA-Q.

The CRC write data is not required because it is

generated by recalculation.

Control

0

1

2

3

4

5

6

7

8

9

78 79 80

95

S0, S1

ADR

DATA-Q

CRC

S0, S1

96 bit

80 bit

bit

QAD3

0

0

0

0

0

0

0

0

1

1

QAD2

0

0

0

0

1

1

1

1

0

0

QAD1

0

0

1

1

0

0

1

1

0

0

QAD0

0

1

0

1

0

1

0

1

0

1

QD7

CTL0

DQ1

DQ9

DQ17

DQ25

DQ33

DQ41

DQ49

DQ57

DQ65

QD6

CTL1

DQ2

DQ10

DQ18

DQ26

DQ34

DQ42

DQ50

DQ58

DQ66

QD5

CTL2

DQ3

DQ11

DQ19

DQ27

DQ35

DQ43

DQ51

DQ59

DQ67

QD4

CTL3

DQ4

DQ12

DQ20

DQ28

DQ36

DQ44

DQ52

DQ60

DQ68

QD3

ADR3

DQ5

DQ13

DQ21

DQ29

DQ37

DQ45

DQ53

DQ61

DQ69

QD2

ADR2

DQ6

DQ14

DQ22

DQ30

DQ38

DQ46

DQ54

DQ62

DQ70

QD1

ADR1

DQ7

DQ15

DQ23

DQ31

DQ39

DQ47

DQ55

DQ63

DQ71

QD0

ADR0

DQ8

DQ16

DQ24

DQ32

DQ40

DQ48

DQ56

DQ64

DQ72

Adderss map for Q data setting beuffer

- Subcode Q data setting process

Initially, data is written to word address range

0000 to 1000, and then data is written to address

1001. Next, only data that needs to be changed

is written if the 91H command QRDY bit is 1, and

then address 1001 is written again. Note that

when shockproof mode is ON, the Q data is

specified according to the data output from the

SM5902AF.

NIPPON PRECISION CIRCUITS-22

SM5902AF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SM5903BF | compression and non compression type shock-proof memory controller |

| SM5903CF | compression and non compression type anti-shock memory controller |

| SM5904BF | compression and non compression type shock-proof memory controller |

| SM5904CF | compression and non compression type |

| SM5905AF | compression and non compression type shock-proof memory controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SM5903BF | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:compression and non compression type shock-proof memory controller |

| SM5903BF_00 | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:compression and non compression type shock-proof memory controller |

| SM5903CF | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:compression and non compression type anti-shock memory controller |

| SM5904BF | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:compression and non compression type shock-proof memory controller |

| SM5904CF | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:compression and non compression type |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。