- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373394 > Si3200-BS (Electronic Theatre Controls, Inc.) DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING PDF資料下載

參數(shù)資料

| 型號: | Si3200-BS |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| 中文描述: | 兩個可編程的CMOS用戶接口與在線監(jiān)測 |

| 文件頁數(shù): | 28/128頁 |

| 文件大小: | 2327K |

| 代理商: | SI3200-BS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

Si3232

28

Preliminary Rev. 0.96

The total power threshold is exceeded (when using

the power calculator method along with the Si3200).

To provide optimal reliability, the device automatically

transitions into the open state until the user changes the

state manually, independent of whether or not the power

alarm interrupt has been masked. The PQ1E to PQ6E

bits of the IRQEN3 register are used to enable the

interrupts for each transistor power alarm, and the

PQ1S to PQ6S bits of the IRQVEC3 register are set

when a power alarm is triggered in the respective

transistor. When using the Si3200, the PQ1E bit is used

to enable the power alarm interrupt, and the PQ1S bit is

set when a Si3200 power alarm is triggered.

4.4.8. Power Dissipation Considerations

The Si3232 relies on the Si3200 to power the line from

the battery supply. The PCB layout and enclosure

conditions should be designed to allow sufficient

thermal dissipation out of the Si3200, and a

programmable power alarm threshold ensures product

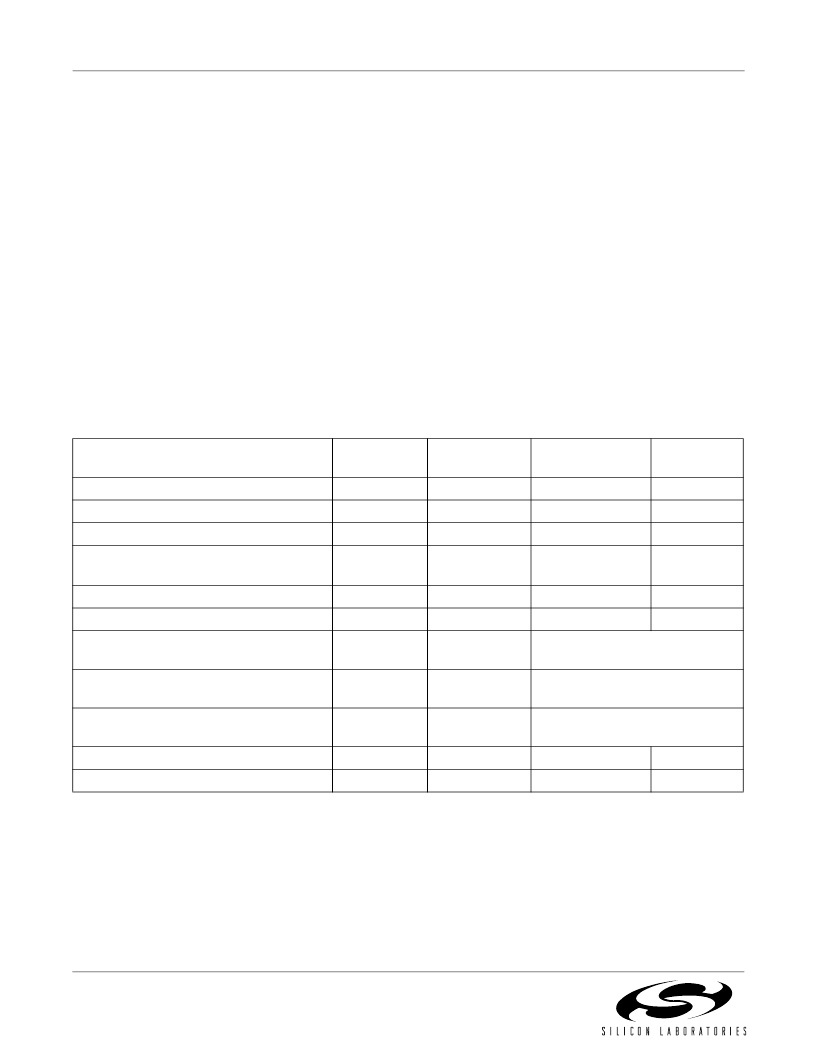

Table 16. Register and RAM Locations used for Power Monitoring and Power Fault Detection

safety under all operating conditions. See “4.4.3. Power

Monitoring and Power Fault Detection” for more details

on power alarm considerations. The Si3200’s thermally-

enhanced SOIC-16 package offers an exposed pad that

improves thermal dissipation out of the package when

soldered to a topside PCB pad connected to inner

power planes. Using appropriate layout practices, the

Si3200 can provide thermal performance of 55 °C/W.

The exposed path should be connected to a low-

impedance ground plane via a topside PCB pad directly

under the part. See package outlines for PCB pad

dimensions. In addition, an opposite-side PCB pad with

multiple vias connecting it to the topside pad directly

under the exposed pad further improves the overall

thermal performance of the system. Refer to “AN55:

Dual ProSLIC User Guide” or the Si3232 evaluation

board data sheet for layout guidelines for optimal

thermal dissipation.

Parameter

Location

Register/RAM

Bits

Measurement

Range

Resolution

Si3200 Power Output Monitor

PSUM

PSUM[15:0]

0 to 34.72 W

1059.6

μ

W

Si3200 Power Alarm Interrupt Pending

IRQVEC3

PQ1S

N/A

N/A

Si3200 Power Alarm Interrupt Enable

IRQEN3

PQ1E

N/A

N/A

Q1/Q2 Power Alarm Threshold (discrete)

Q1/Q2 Power Alarm Threshold (Si3200)

PTH12

PTH12[15:0]

0 to 16.319 W

0 to 34.72 W

498

μ

W

1059.6

μ

W

31.4

μ

W

498

μ

W

Q3/Q4 Power Alarm Threshold

PTH34

PTH34[15:0]

0 to 1.03 W

Q5/Q6 Power Alarm Threshold

PTH56

PTH56[15:0]

0 to 16.319 W

Q1/Q2 Thermal LPF Pole

PLPF12

PLPF12[15:3]

See “4.4.6. Power Filter and

Alarms”

Q3/Q4 Thermal LPF Pole

PLPF34

PLPF34[15:3]

See “4.4.6. Power Filter and

Alarms”

Q5/Q6 Thermal LPF Pole

PLPF56

PLPF56[15:3]

See “4.4.6. Power Filter and

Alarms”

Q1–Q6 Power Alarm Interrupt Pending

IRQVEC3

TBD

N/A

Q71–Q6 Power Alarm Interrupt Enable

IRQEN3

TBD

N/A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Si3232 | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3200-KS | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3200-X-FS | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3200-X-GS | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3232-X-FQ | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI3200-BSR | 制造商:Silicon Laboratories Inc 功能描述: |

| SI3200-FS | 功能描述:電信線路管理 IC 100 V Linefeed Interface IC unit RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| SI3200-FSR | 制造商:Silicon Laboratories Inc 功能描述:SLIC 2CH 70DB 45MA 3.3V/5V 16SOIC EP - Tape and Reel |

| Si3200-G-FS | 功能描述:射頻無線雜項 100 V Linefeed Inter IC unit price RoHS:否 制造商:Texas Instruments 工作頻率:112 kHz to 205 kHz 電源電壓-最大:3.6 V 電源電壓-最小:3 V 電源電流:8 mA 最大功率耗散: 工作溫度范圍:- 40 C to + 110 C 封裝 / 箱體:VQFN-48 封裝:Reel |

| SI3200-G-FSR | 功能描述:電信線路管理 IC 100 V Linefeed Interface RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。