- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373394 > SI3014 (Electronic Theatre Controls, Inc.) GLOBAL MC 97 SILICON DAA PDF資料下載

參數(shù)資料

| 型號: | SI3014 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | GLOBAL MC 97 SILICON DAA |

| 中文描述: | 全球三菱商事97硅DAA |

| 文件頁數(shù): | 32/54頁 |

| 文件大小: | 1407K |

| 代理商: | SI3014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Si3035

32

Rev. 1.2

Revision Identification

The Si3035 provides the system designer the ability to

determine the revision of the Si3021 and/or the Si3012.

Register 11 identifies the revision of the Si3021 with 4

bits named REVA. Register 13 identifies the revision of

the Si3012 with 4 bits named REVB. Table 19 shows

the values for the various revisions.

Calibration

The Si3035 initiates an auto-calibration by default

whenever the device goes off-hook or experiences a

loss in line power. Calibration is used to remove any

offsets that may be present in the on-chip A/D converter

which

could

affect

the

Auto-calibration is typically initiated after the DAA DC

termination stabilizes and takes 512/Fs seconds to

complete. Due to the large variation in line conditions

and line card behavior that may be presented to the

DAA, it can be beneficial to use manual calibration in

lieu of auto-calibration. Manual calibration should be

executed as close as possible to 512/Fs seconds before

valid transmit/receive data is expected.

The following steps should be taken to implement

manual calibration:

1. The CALD (auto-calibration disable—Register 17) bit must

be set to 1.

2. The MCAL (manual calibration) bit must be toggled to 1

and then 0 to begin and complete the calibration.

3. The calibration will be completed in 512/Fs seconds.

In-Circuit Testing

The Si3035’s advanced design provides the modem

manufacturer with an increased ability to determine

system functionality during production line tests, as well

as support for end-user diagnostics. Four loopback

modes exist allowing increased coverage of system

components. For three of the test modes, a line-side

power source is needed. While a standard phone line

A/D

dynamic

range.

can be used, the test circuit in Figure 1 on page 4 is

adequate. In addition, an off-hook sequence must be

performed to connect the power source to the line-side

chip.

For the start-up test mode, no line-side power is

necessary and no off-hook sequence is required. The

start-up test mode is enabled by default. When the PDL

bit (Register 6, bit 4) is set (the default case), the line

side is in a power-down mode and the DSP-side is in a

digital loop-back mode. In this mode, data received on

SDI is passed through the internal filters and

transmitted on SDO. This path will introduce

approximately 0.9 dB of attenuation on the SDI signal

received. The group delay of both transmit and receive

filters will exist between SDI and SDO. Clearing the

PDL bit disables this mode and the SDO data is

switched to the receive data from the line side. When

the PDL bit is cleared the FDT bit (Register 12, bit 6) will

become

active,

indicating

communication between the line-side and DSP-side.

This can be used to verify that the ISOcap link is

operational.

The remaining test modes require an off-hook sequence

to operate. The following sequence defines the off-hook

requirement:

1. Power up or reset.

2. Program clock generator to desired sample rate.

3. Enable line-side by clearing PDL bit.

4. Issue off-hook

5. Delay 1548/Fs to allow calibration to occur.

6. Set desired test mode.

The ISOcap digital loopback mode allows the data

pump to provide a digital input test pattern on SDI and

receive that digital test pattern back on SDO. To enable

this mode, set the DL bit of Register 1. In this mode, the

isolation barrier is actually being tested. The digital

stream is delivered across the isolation capacitor, C1 of

Figure 16 on page 15, to the line-side device and

returned across the same barrier. In this mode, the

0.9 dB attenuation and filter group delays also exist.

The analog loopback mode allows an external device to

drive the RX pin of the line-side chip and receive the

signal from the TX pin. This mode allows testing of

external components connecting the RJ-11 jack (TIP

and RING) to the line side of the Si3035. To enable this

mode, set the AL bit of Register 2.

The final testing mode, internal analog loopback, allows

the system to test the basic operation of the

transmit/receive path of the line side and the external

components R4, R18, R21, and C5 of Figure 16 on

page 15. In this test mode, the data pump provides a

the

successful

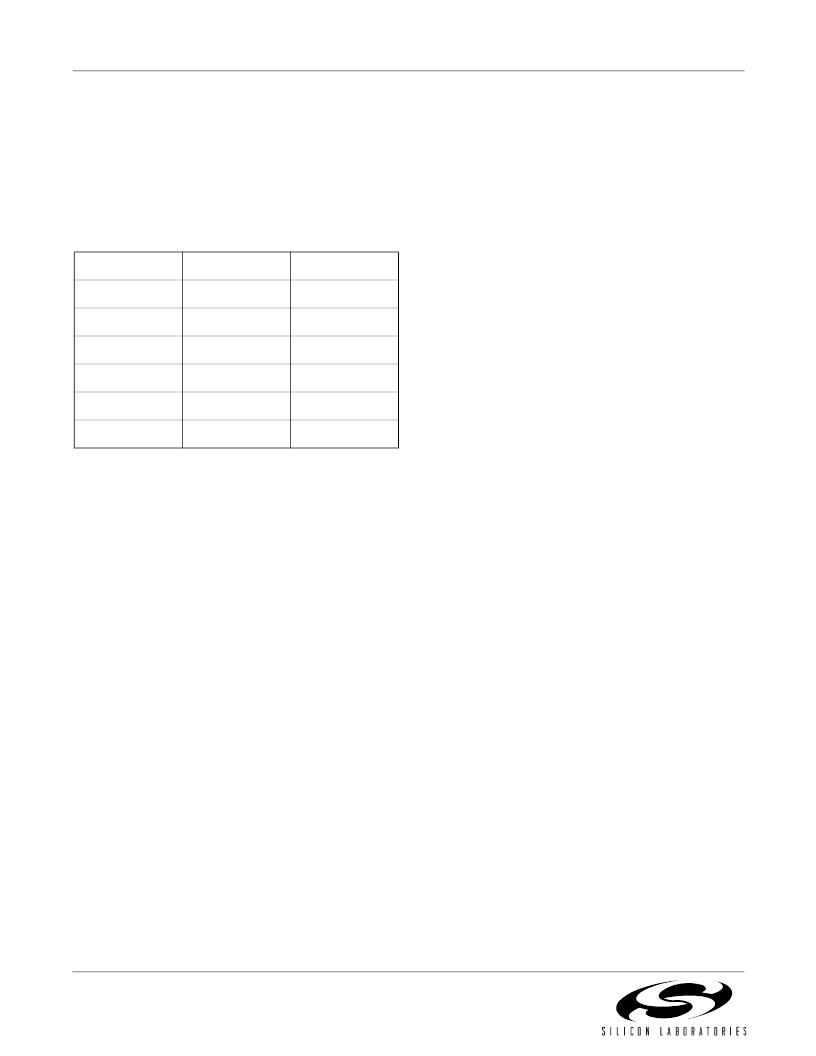

Table 19. Revision Values

Revision

Si3021

Si3012

A

1000

—

B

1001

—

C

1010

—

D

—

0100

E

—

0101

G

—

0111

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SI3025 | COOLER FOR TO-3 20 WATTS |

| Si3200-BS | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3232 | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3200-KS | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

| Si3200-X-FS | DUAL PROGRAMMABLE CMOS SLIC WITH LINE MONITORING |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI-30140-F | 制造商:Bel Fuse 功能描述:- Trays |

| Si3014-C-FS | 功能描述:射頻無線雜項(xiàng) Si3034 Global DAA RoHS:否 制造商:Texas Instruments 工作頻率:112 kHz to 205 kHz 電源電壓-最大:3.6 V 電源電壓-最小:3 V 電源電流:8 mA 最大功率耗散: 工作溫度范圍:- 40 C to + 110 C 封裝 / 箱體:VQFN-48 封裝:Reel |

| SI3014-C-FSR | 制造商:Silicon Laboratories Inc 功能描述:SI3034 GLOBAL DAA LINE-SIDE-LE - Tape and Reel |

| Si3014-KS | 功能描述:電信線路管理 IC Si3034 Global DAA SSI interface RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| SI3014-KSR | 制造商:Silicon Laboratories Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。