- 您現(xiàn)在的位置:買賣IC網 > PDF目錄378684 > SAA7134HL (NXP Semiconductors N.V.) PCI audio and video broadcast decoder PDF資料下載

參數資料

| 型號: | SAA7134HL |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 通用總線功能 |

| 英文描述: | PCI audio and video broadcast decoder |

| 文件頁數: | 9/51頁 |

| 文件大小: | 233K |

| 代理商: | SAA7134HL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

SAA7134HL_4

Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Product data sheet

Rev. 04 — 31 March 2006

9 of 51

Philips Semiconductors

SAA7134HL

PCI audio and video broadcast decoder

[1]

PCI-bus pins are located on the long side of the package to simplify PCI board layout requirements.

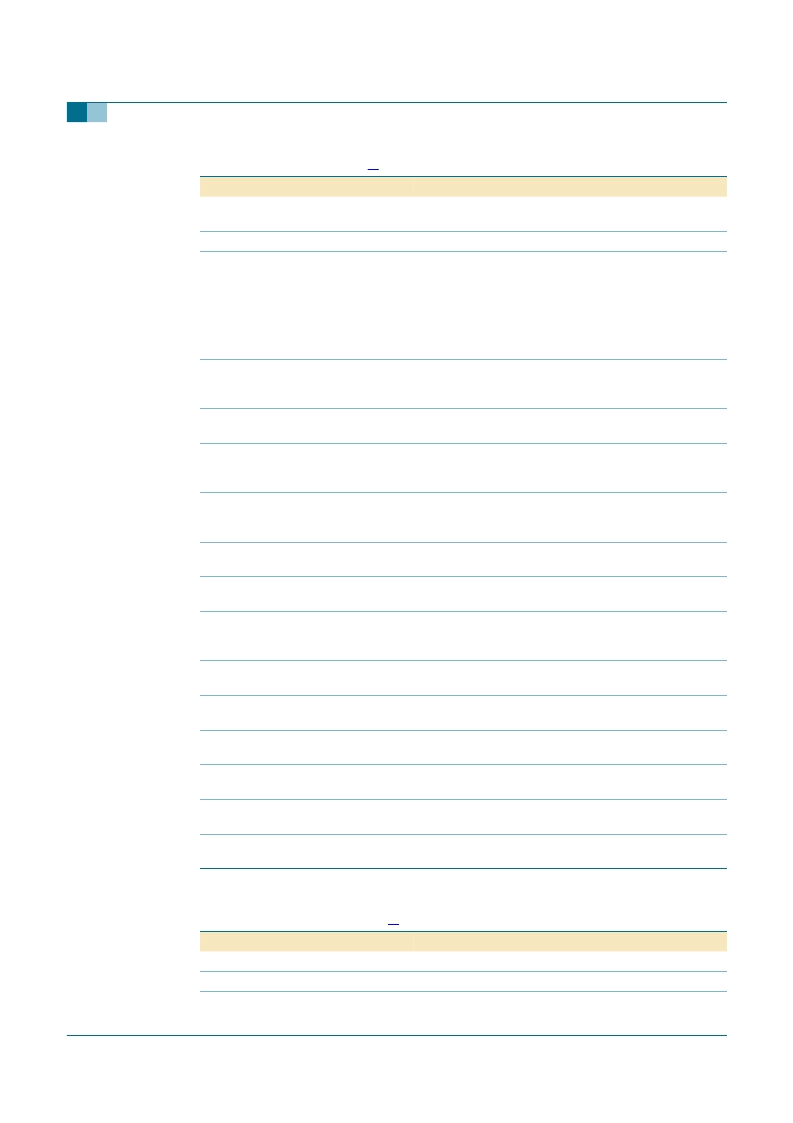

Table 5:

Symbol

PCI_CLK

PCI interface pins

[1]

Pin

40

Type

PI

Description

PCI clock input: reference for all bus transactions, up to

33.33 MHz

PCI reset input: will 3-state all PCI pins (active LOW)

multiplexed address and data input or output:

bi-directional, 3-state

PCI_RST#

AD[31] to AD[00] 4 to 11,

127

PI

PIOand

T/S

14 to 18,

21 to 23,

34 to 37,

41 to 44

and

46 to 53

12, 24,

33

and 45

32

C/BE[3]# to

C/BE[0]#

PIOand

T/S

command code input or output: indicates type of

requested transaction and byte enable, for byte aligned

transactions (active LOW)

parity input or output: driven by the data source, even

parity over all pins AD and C/BE#

frame input or output: driven by the current bus master

(owner), to indicate the beginning and duration of a bus

transaction (active LOW)

target ready input or output: driven by the addressed

target, to indicate readiness for requested transaction

(active LOW)

initiator ready input or output: driven by the initiator, to

indicate readiness to continue transaction (active LOW)

stop input or output: target is requesting the master to

stop the current transaction (active LOW)

initialization device select input: this input is used to select

the SAA7134HL during configuration read and write

transactions

device select input or output: driven by the target device,

to acknowledge address decoding (active LOW)

PCI request output: the SAA7134HL requests master

access to PCI-bus (active LOW)

PCI grant input: the SAA7134HL is granted to master

access PCI-bus (active LOW)

interrupt A output: this pin is an open-drain interrupt

output, conditions assigned by the interrupt register

parity error input or output: the receiving device detects

data parity error (active LOW)

system error output: reports address parity error (active

LOW)

PAR

PIOand

T/S

PIOand

S/T/S

FRAME#

25

TRDY#

27

PIOand

S/T/S

IRDY#

26

PIOand

S/T/S

PIOand

S/T/S

PI

STOP#

29

IDSEL

13

DEVSEL#

28

PIOand

S/T/S

PO

REQ#

3

GNT#

2

PI

INT_A

126

PO and

O/D

PIOand

S/T/S

PO and

O/D

PERR#

30

SERR#

31

Table 6:

Symbol

XTALI

XTALO

LEFT2

Analog interface pins

[1]

Pin

62

63

94

Type

CI

CO

AI

Description

quartz oscillator input: 32.11 MHz or 24.576 MHz

quartz oscillator output

analog audio stereo left 2 input or mono input

相關PDF資料 |

PDF描述 |

|---|---|

| SAA7134HL | PCI audio and video broadcast decoder |

| SAA7134HL | PCI audio and video broadcast decoder |

| SAA7160E | PCI Express based audio and video bridge |

| SAA7160ET | PCI Express based audio and video bridge |

| SAA7706H | Car radio Digital Signal Processor (DSP) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SAA7134HL/V1,518 | 功能描述:視頻 IC PCI 9-BIT VID/STEREO RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7134HL/V1,557 | 功能描述:視頻 IC PCI 9-BIT VID/STEREO RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7134HLBE | 功能描述:視頻 IC PCI 9-BIT VID/STEREO DECODER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7134HLBE-T | 功能描述:視頻 IC PCI 9-BIT VID/STEREO DECODER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7135 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single-chip, analog TV video/stereo DECODER |

發(fā)布緊急采購,3分鐘左右您將得到回復。