- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372110 > SAA5281GP (NXP SEMICONDUCTORS) RES 11.3K OHM 1/16W .5% 0603 SMD PDF資料下載

參數(shù)資料

| 型號: | SAA5281GP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 圖文 |

| 英文描述: | RES 11.3K OHM 1/16W .5% 0603 SMD |

| 中文描述: | TELETEXT AND VPS/PDC DECODER, PQFP64 |

| 封裝: | 14 X 20 MM, 2.80 MM HEIGHT, PLASTIC, SOT-319-2, QFP-64 |

| 文件頁數(shù): | 20/48頁 |

| 文件大小: | 1187K |

| 代理商: | SAA5281GP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

1996 Nov 04

20

Philips Semiconductors

Preliminary specification

Integrated Video input processor and

Teletext decoder (IVT1.8*)

SAA5281

VPT data memory organization

To simplify the software for dual-standard VPT decoders,

the VPS data from line 16 is stored in row 25 of Chapter 5

of the page memory, and is aligned to match the

packet 8/30 format 2 data as far as possible. The 8/30

format 2 packet is Hamming coded and by setting the

appropriate register control bit the data is stored after

hardware Hamming correction. There are 4 data bits

stored in each column address of memory with an

additional Hamming error bit. The data equivalent to the

VPS signal is found in columns 12 to 19.

Although the VPS data is not Hamming protected, it is

stored with 4 data bits per column address in the same

way with an additional biphase error bit. The extra space

in Row 25 is allocated to two more Line 16 words.

They are Word 15 (reserved) and Word 4 (Program

Source Identification, ASCII sequential) which may be

useful for future applications. Details of the memory

organization are shown in Fig.12.

The stored data can be read from memory via the I

2

C-bus

in the normal way. Multiple reception/majority error

correction of the VPS data is the responsibility of the

control software, the device simply stores the data as

transmitted after biphase decoding.

As both VPS and 8/30/2 signals are stored in separate

memory locations, it is possible to deal with future

situations where both System A and System B

transmissions may be present on the same TV channel,

the defaults and level of service chosen by the control

software.

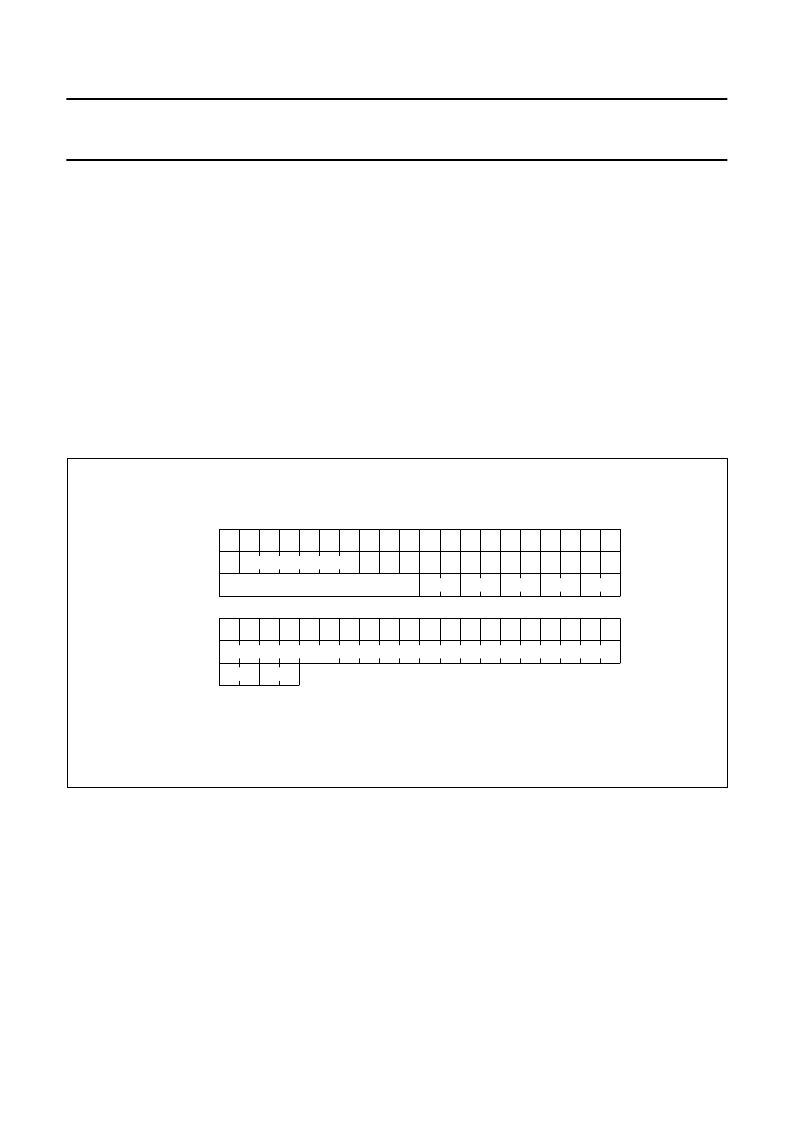

Fig.12 Detailed memory organization.

handbook, full pagewidth

MBD787

2

1

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

B11

B12

B13

B14

B15

b13 b14 b15 b16 b17 b18 b19 b20 b21 b22 b23 b24 b25

initial page

D

received page information

column

8/30/2

VPS

22

21

23

24

25

26

27

28

29

30

11

12

13

14

15

16

17

18

19

column

8/30/2

VPS

0

20

status display

B4

B5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA5281P | Integrated Video input processor and Teletext decoder IVT1.8 |

| SAA5281ZP | Integrated Video input processor and Teletext decoder IVT1.8 |

| SAA5284GP | Multimedia video data acquisition circuit |

| SAA5284 | Multimedia video data acquisition circuit |

| SAA5288 | TV Microcontroller with Full Screen On Screen Display (OSD)(帶全屏屏幕顯示的TV微控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA5281P | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated Video input processor and Teletext decoder IVT1.8 |

| SAA5281ZP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated Video input processor and Teletext decoder IVT1.8 |

| SAA5284 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multimedia video data acquisition circuit |

| SAA5284GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multimedia video data acquisition circuit |

| SAA5288 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:TV microcontroller with full screen On Screen Display OSD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。