- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385813 > SAA2013H (NXP SEMICONDUCTORS) Adaptive allocation and scaling for PASC coding in DCC systems PDF資料下載

參數(shù)資料

| 型號: | SAA2013H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | Adaptive allocation and scaling for PASC coding in DCC systems |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封裝: | PLASTIC, SOT-307-2, QFP-44 |

| 文件頁數(shù): | 9/32頁 |

| 文件大小: | 137K |

| 代理商: | SAA2013H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

May 1994

9

Philips Semiconductors

Preliminary specification

Adaptive allocation and scaling for PASC

coding in DCC systems

SAA2013

For each sub-band frame, SAA2013 calculates the

allocation and scale factor index information required by

the SAA2003. In order to synchronize the codec part of

SAA2003, SAA2013 frequently requests status

information from the codec. It monitors sample frequency,

emphasis information and stereo mode, and uses the

ready-to-receive bit of the codec to determine when to

transfer information.

Decode mode

In decode the SAA2003 will transfer samples from FDAI to

FDAO with a delay of 480 FDWS periods. Settings and

status information can be sent to SAA2003 via SAA2013,

but the SAA2013 does not itself act on this information.

Transfer of this information is automatically synchronized

to the ready-to-receive bit of SAA2003 by SAA2013.

Audio sample resolution section

The SAA2013 is designed for operation with audio input

sources of 14, 15, 16 or 18-bit resolution.

For optimum audio performance the bit allocation

algorithm of the SAA2013 can be varied to suit the bit

resolution of the audio source. This is done with the pins

RESOL0 and RESOL1 as shown in Table 1.

Table 1

Resolution set by pins RESOL0 and RESOL1.

RESOLUTION

RESOL0

RESOL1

16 bits

18 bits

14 bits

15 bits

0

0

1

1

0

1

0

1

Filtered data interface

The filtered data interface signals are given in Table 2.

Table 2

Filtered data interface signals.

PIN

INPUT/OUTPUT

FUNCTION

FREQUENCY

FDWS

FDCL

FDAI

FDAO

FSYNC

input

input

input

output

input

filtered data interface word select

filtered data interface bit clock

filtered data input

filtered data output

filtered data sub-band synchronization

f

s

64f

s

The filtered data interface transfers sub-band filtered

samples between the stereo filter codec SAA2003 and

SAA2013. The interface is similar to a normal I

2

S interface,

consisting of clock (FDCL), data (FDAI/FDAO) and word

select lines (FDWS), except that the samples sent

represent signals divided into 32 sub-bands. One frame of

data consists of 12 samples from 32 sub-bands for both

left and right channels, i.e.: 768 audio samples. Each

audio sub-band sample is represented by a 24-bit two’s

complement number.

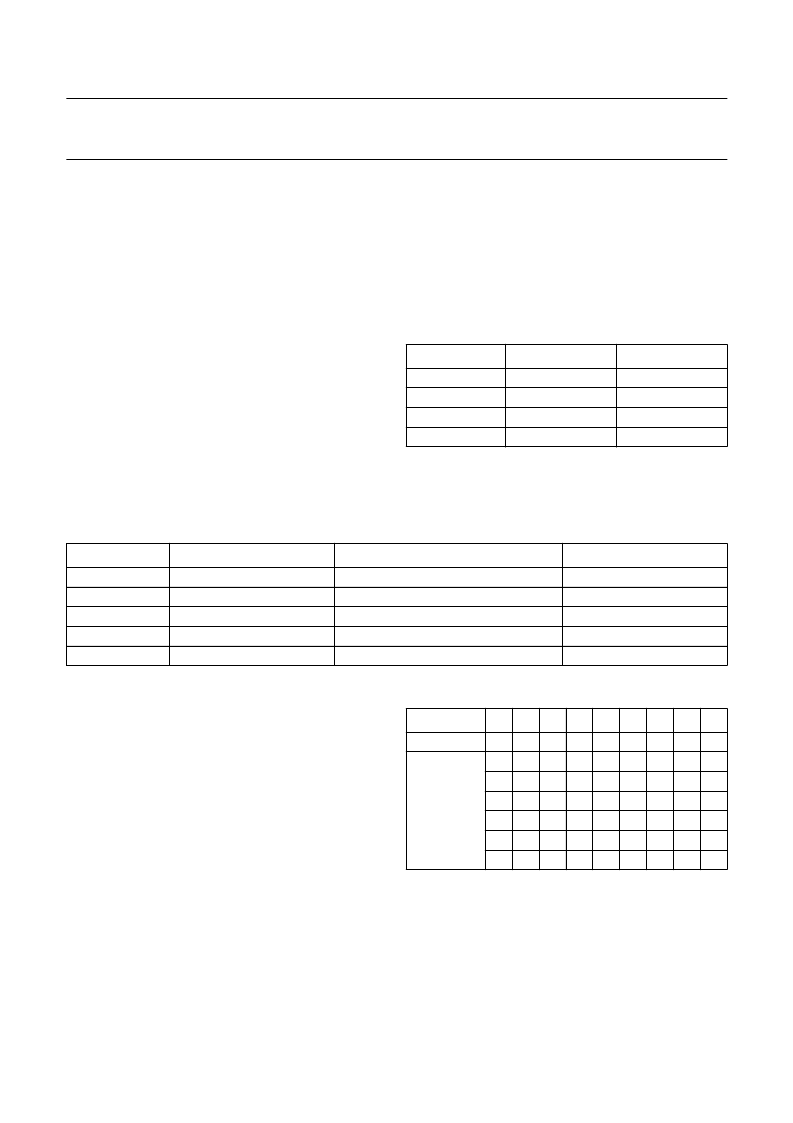

The order in which the samples are sent is shown in

Table 3.

For two channel mono, the order is the same, but with

Channel 1 samples in the place of left and Channel 2

samples in place of right.

Table 3

Order of samples.

The signal FSYNC is used between each PASC frame to

indicate the sending of samples for sub-band 0 (Fig.7).

SUB-BAND

0

0

1

1

2

2

...

31

31

Channel

Sample

L

0

1

2

.

.

11

R

0

1

2

.

.

11

L

0

1

2

.

.

11

R

0

1

2

.

.

11

L

0

1

2

.

.

11

R

0

1

2

.

.

11

...

...

...

...

...

...

...

L

0

1

2

.

.

11

R

0

1

2

.

.

11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA2022 | Tape formatting and error correction for the DCC system |

| SAA2022GP | Tape formatting and error correction for the DCC system |

| SAA4995WP | Panorama-IC (PAN-IC)(全景畫面IC) |

| SAA55XX | TV microcontrollers with Closed Captioning (CC) and On-Screen Display (OSD) |

| SAA6712E | ECONOLINE: RB & RA - Dual Output from a Single Input Rail- Power Sharing on Output- Industry Standard Pinout- 1kVDC & 2kVDC Isolation- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 85% |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA2013HB-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Audio Tape Circuit |

| SAA2022 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Tape formatting and error correction for the DCC system |

| SAA2022GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Tape formatting and error correction for the DCC system |

| SAA2023 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Drive processor for DCC systems |

| SAA2023GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Drive processor for DCC systems |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。