- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372099 > S87C654-5F40 (NXP SEMICONDUCTORS) CMOS single-chip 8-bit microcontroller PDF資料下載

參數(shù)資料

| 型號: | S87C654-5F40 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CMOS single-chip 8-bit microcontroller |

| 中文描述: | 8-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| 文件頁數(shù): | 8/24頁 |

| 文件大小: | 258K |

| 代理商: | S87C654-5F40 |

Philips Semiconductors

Product specification

83C654

CMOS single-chip 8-bit microcontroller

1998 Jan 06

8

ROM CODE PROTECTION

(83C654)

The 83C654 has an additional security

feature. ROM code protection may be

selected by setting a mask–programmable

security bit (i.e., user dependent). This

feature may be requested during ROM code

submission. When selected, the ROM code

is protected and cannot be read out at any

time by any test mode or by any instruction in

the external program memory space.

The MOVC instructions are the only

instructions that have access to program

code in the internal or external program

memory. The EA input is latched during

RESET and is “don’t care” after RESET

(also if the security bit is not set). This

implementation prevents reading internal

program code by switching from external

program memory to internal program memory

during a MOVC instruction or any other

instruction that uses immediate data.

OSCILLATOR

CHARACTERISTICS

XTAL1 and XTAL2 are the input and output,

respectively, of an inverting amplifier. The

pins can be configured for use as an on-chip

oscillator, as shown in the Logic Symbol,

page 3.

To drive the device from an external clock

source, XTAL1 should be driven while XTAL2

is left unconnected. There are no

requirements on the duty cycle of the

external clock signal, because the input to

the internal clock circuitry is through a

divide-by-two flip-flop. However, minimum

and maximum high and low times specified in

the data sheet must be observed.

Reset

A reset is accomplished by holding the RST

pin high for at least two machine cycles (24

oscillator periods), while the oscillator is

running. To insure a good power-on reset, the

RST pin must be high long enough to allow

the oscillator time to start up (normally a few

milliseconds) plus two machine cycles. At

power-on, the voltage on V

DD

and RST must

come up at the same time for a proper

start-up.

Idle Mode

In the idle mode, the CPU puts itself to sleep

while all of the on-chip peripherals stay

active. The instruction to invoke the idle

mode is the last instruction executed in the

normal operating mode before the idle mode

is activated. The CPU contents, the on-chip

RAM, and all of the special function registers

remain intact during this mode. The idle

mode can be terminated either by any

enabled interrupt (at which time the process

is picked up at the interrupt service routine

and continued), or by a hardware reset which

starts the processor in the same manner as a

power-on reset.

Power-Down Mode

In the power-down mode, the oscillator is

stopped and the instruction to invoke

power-down is the last instruction executed.

Only the contents of the on-chip RAM are

preserved. A hardware reset is the only way

to terminate the power-down mode. The

control bits for the reduced power modes are

in the special function register PCON. Table 2

shows the state of the I/O ports during low

current operating modes.

I

2

C SERIAL COMMUNICATION —

SIO1

The I

2

C serial port is identical to the I

2

C

serial port on the 8XC552. The operation of

this subsystem is described in detail in the

8XC552 section of this manual.

Note that in both the 8XC652/4 and the

8XC552 the I

2

C pins are alternate functions

to port pins P1.6 and P1.7. Because of this,

P1.6 and P1.7 on these parts do not have a

pull-up structure as found on the 80C51.

Therefore P1.6 and P1.7 have open drain

outputs on the 8XC652/4.

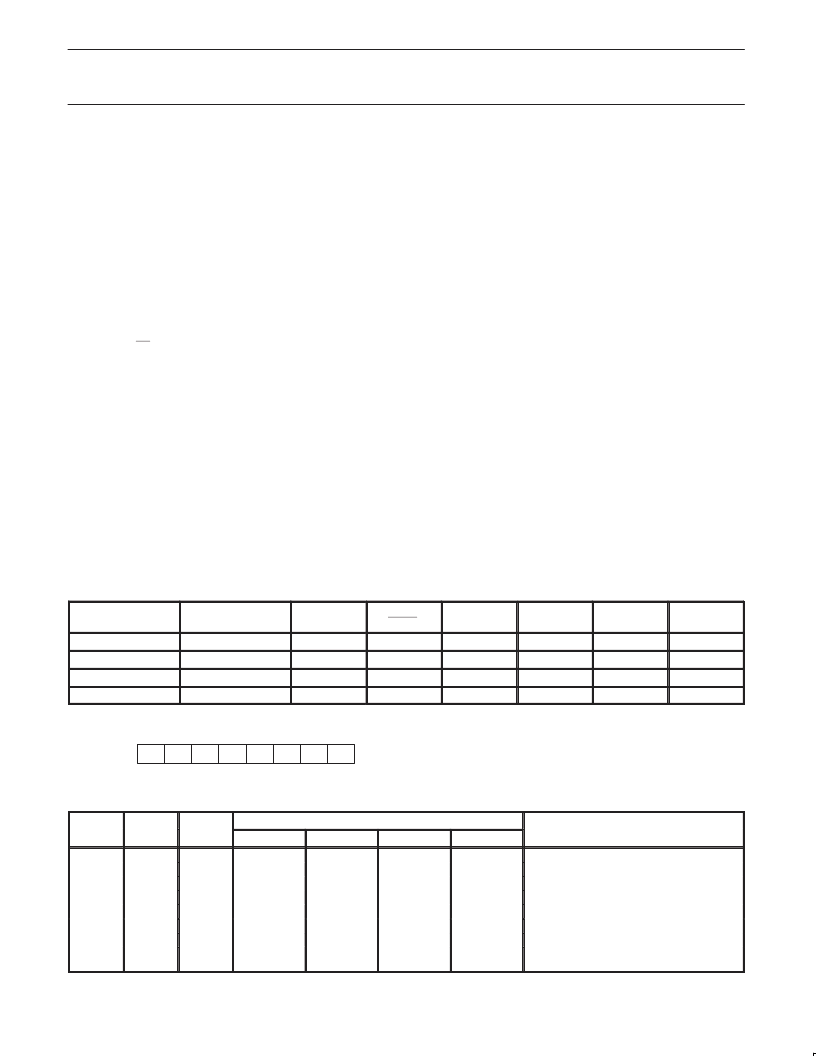

Table 2.

External Pin Status During Idle and Power-Down Mode

MODE

PROGRAM

MEMORY

ALE

PSEN

PORT 0

PORT 1

PORT 2

PORT 3

Idle

Internal

1

1

Data

Data

Data

Data

Idle

External

1

1

Float

Data

Address

Data

Power-down

Internal

0

0

Data

Data

Data

Data

Power-down

External

0

0

Float

Data

Data

Data

Serial Control Register (S1CON) – See Table 3

CR2

ENS1

STA

STO

SI

AA

CR1

CR0

S1CON (D8H)

Bits CR0, CR1 and CR2 determine the serial clock frequency that is generated in the master mode of operation.

Table 3.

Serial Clock Rates

BIT FREQUENCY (kHz) AT f

OSC

6MHz

12MHz

23

47

27

54

31.25

62.5

37

75

6.25

12.5

50

100

100

200

1

0.24 < 62.5

0 to 255

0 to 254

CR2

0

0

0

0

1

1

1

1

CR1

0

0

1

1

0

0

1

1

CR0

0

1

0

1

0

1

0

1

16MHz

62.5

71

83.3

100

17

133

1

267

1

0.65 < 55.6

0 to 253

24MHz

94

107

1

125

1

150

1

25

200

1

400

1

0.98 < 50.0

0 to 251

f

OSC

DIVIDED BY

256

224

192

160

960

120

60

96

×

(256 – (reload value Timer 1))

reload value range Timer 1 (in mode 2)

0.49 < 62.5

NOTES:

1. These frequencies exceed the upper limit of 100kHz of the I

2

C-bus specification and cannot be used in an I

2

C-bus application.

相關PDF資料 |

PDF描述 |

|---|---|

| S87C654-7N40 | CMOS single-chip 8-bit microcontroller |

| S87C752-5A28 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S87C752-5N28 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM, 5 channel 8 bit A/D, I2C, PWM, low pin count |

| S87L51FA-5K44 | 8-BIT MICROCONTROLLER |

| S87L51FA-8K44 | 8-BIT MICROCONTROLLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| S87C654-5K44 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| S87C654-5N40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller |

| S87C654-7 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit microcontroller 8K/16K, 256 OTP, I2C |

| S87C654-7A44 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller |

| S87C654-7B44 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。