- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368610 > S1D2511B01 (SAMSUNG SEMICONDUCTOR CO. LTD.) DEFLECTION PROCESSOR FOR MULTISYNC MONITORS PDF資料下載

參數(shù)資料

| 型號: | S1D2511B01 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| 中文描述: | 偏轉(zhuǎn)處理器多同步監(jiān)測儀 |

| 文件頁數(shù): | 24/34頁 |

| 文件大小: | 330K |

| 代理商: | S1D2511B01 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

S1D2511B01 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

24

free running frequency(fo) adjustment.

Sending the desired fo on the sync input and progressively decreasing the free running frequently I

2

C register

value(address 02), the HLOCKOUT Pin will go high as soon as the proper setting is reached. Setting the free run-

ning frequency this way allows to fully exploit the S1D2511B01 horizontal frequency range.

HORIZONTAL PART

Internal input conditions

Horizontal part is internally fed by synchro processor with a digital signal corresponding to horizontal synchro

pulses or to TTL composite input.

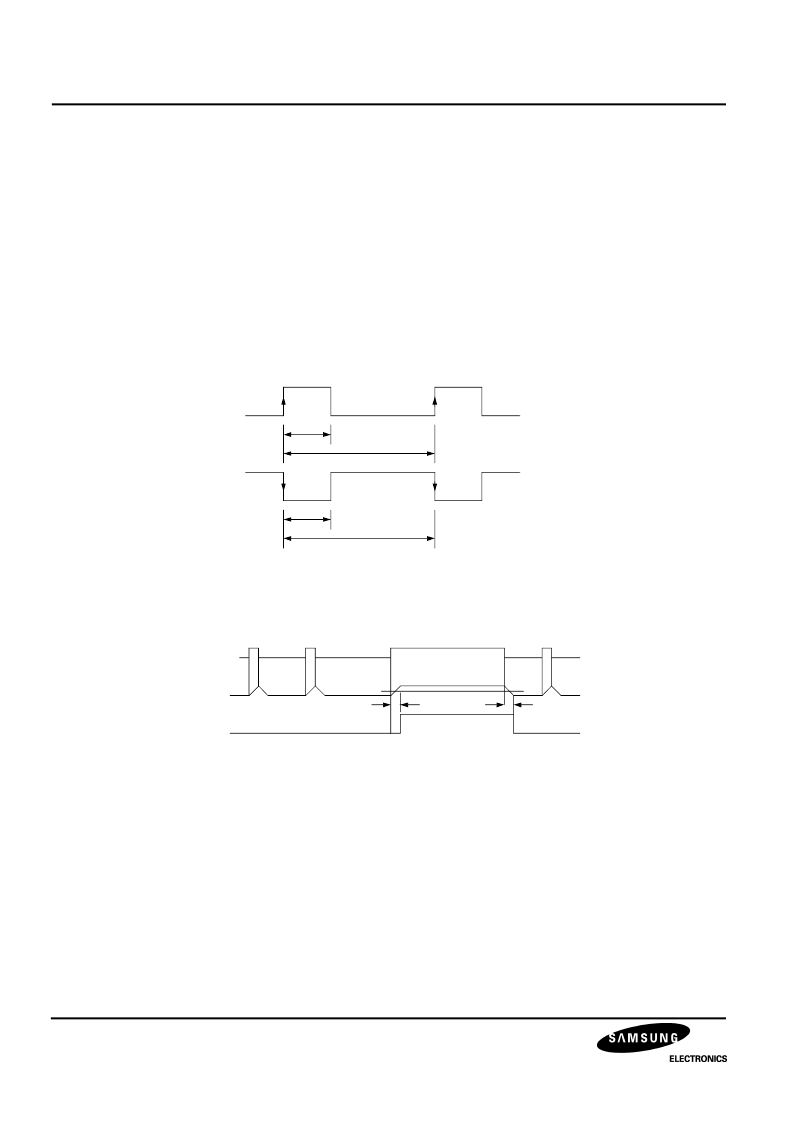

concerning the duty cycle of the input signal, the following signals (positive or negative)may be applied to the

circuit.

Using internal integration, both signals are recognized on condition that Z/T < 25%, synchronisation occurs on the

leading edge of the internal sync signal. The minimum value of Z is 0.7

μ

s.

Figure 6.

An other integration is able to extract vertical pulse of composite synchro if duty cycle is more than 25% (typically

d = 35%)

(7)

Figure 7.

The last feature performed is the equalizing pulses removing to avoid parasitic pulse on phase comparator input

which is intolerent to wrong or missing pulse.

PLL1

The PLL1 is composed of a phase comparator, an external filter and a voltage control oscillator (VCO).

The phase comparator is a phase frequency type designed in CMOS technology. This kind of phase detector

avoids locking on false frequencies. It is followed by a charge pump, composed of two current sources sunk and

sourced (I = 1mA typ. when locked, I = 140mA when unlocked). This difference between lock/unlock permits a

smooth catching of horizontal frequency by PLL1. This effect is reinforced by an internal original slow down system

when PLL1 is locked avoiding horizontal too fast frequency change.

The dynamic bahaviour of the PLL is fixed by an external filter which integrates the current of the charge pump.

A CRC filter is generally used (see figure 8 )

Z

T

Z

d

d

c

TRAMEXT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1D2511B01-A0B0 | DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| S1D2514X01 | SDR Cable Assembly; Connector Type A:micro D Ribbon Plug; Connector Type B:micro D Ribbon Plug; Cable Length:2m; No. of Contacts:26; Pitch Spacing:0.8mm RoHS Compliant: Yes |

| S1D2518X01 | DB25 RJ11,4 WIRE ONLY. FEMAL |

| S1L9226X | RF AMP & SERVO SIGNAL PROCESSOR |

| S1L9226X01-Q0R0 | RF AMP & SERVO SIGNAL PROCESSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1D2511B01-A0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| S1D2511B01-A0B0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| S1D2511C01-AO | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| S1D2512X01 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| S1D2512X01-A0B0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。