- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98068 > S1C63455F 4-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PQFP128 PDF資料下載

參數(shù)資料

| 型號: | S1C63455F |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PQFP128 |

| 封裝: | PLASTIC, QFP5-128 |

| 文件頁數(shù): | 5/119頁 |

| 文件大小: | 865K |

| 代理商: | S1C63455F |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

with DATA SLICER and ON-SCREEN DISPLAY CONTROLLER

MITSUBISHI MICROCOMPUTERS

101

Rev. 1.0

M306H1SFP

Item

Specification

Transfer data format

Transfer data length: 8 bits

Transfer clock

When internal clock is selected (bit 3 at addresses 03A016, 03A816, 037816

= “0”) : fi/ 2(n+1) (Note 1)

fi = f1, f8, f32

When external clock is selected (bit 3 at addresses 03A016, 03A816, 037816

= “1”) : Input from CLKi pin

Transmission/reception control

CTS function/RTS function/CTS, RTS function chosen to be invalid

Transmission start condition

To start transmission, the following requirements must be met:

_ Transmit enable bit (bit 0 at addresses 03A516, 03AD16, 037D16) = “1”

_ Transmit buffer empty flag (bit 1 at addresses 03A516, 03AD16, 037D16) = “0”

_______

_ When CTS function selected, CTS input level = “L”

Furthermore, if external clock is selected, the following requirements must also be met:

_ CLKi polarity select bit (bit 6 at addresses 03A416, 03AC16, 037C16) = “0”:

CLKi input level = “H”

_ CLKi polarity select bit (bit 6 at addresses 03A416, 03AC16, 037C16) = “1”:

CLKi input level = “L”

Reception start condition

To start reception, the following requirements must be met:

_ Receive enable bit (bit 2 at addresses 03A516, 03AD16, 037D16) = “1”

_ Transmit enable bit (bit 0 at addresses 03A516, 03AD16, 037D16) = “1”

_ Transmit buffer empty flag (bit 1 at addresses 03A516, 03AD16, 037D16) = “0”

Furthermore, if external clock is selected, the following requirements must

also be met:

_ CLKi polarity select bit (bit 6 at addresses 03A416, 03AC16, 037C16) = “0”:

CLKi input level = “H”

_ CLKi polarity select bit (bit 6 at addresses 03A416, 03AC16, 037C16) = “1”:

CLKi input level = “L”

When transmitting

_ Transmit interrupt cause select bit (bits 0, 1 at address 03B016, bit 4 at

address 037D16) = “0”: Interrupts requested when data transfer from UARTi

transfer buffer register to UARTi transmit register is completed

_ Transmit interrupt cause select bit (bits 0, 1 at address 03B016, bit 4 at

address 037D16) = “1”: Interrupts requested when data transmission from

UARTi transfer register is completed

When receiving

_ Interrupts requested when data transfer from UARTi receive register to

UARTi receive buffer register is completed

Error detection

Overrun error (Note 2)

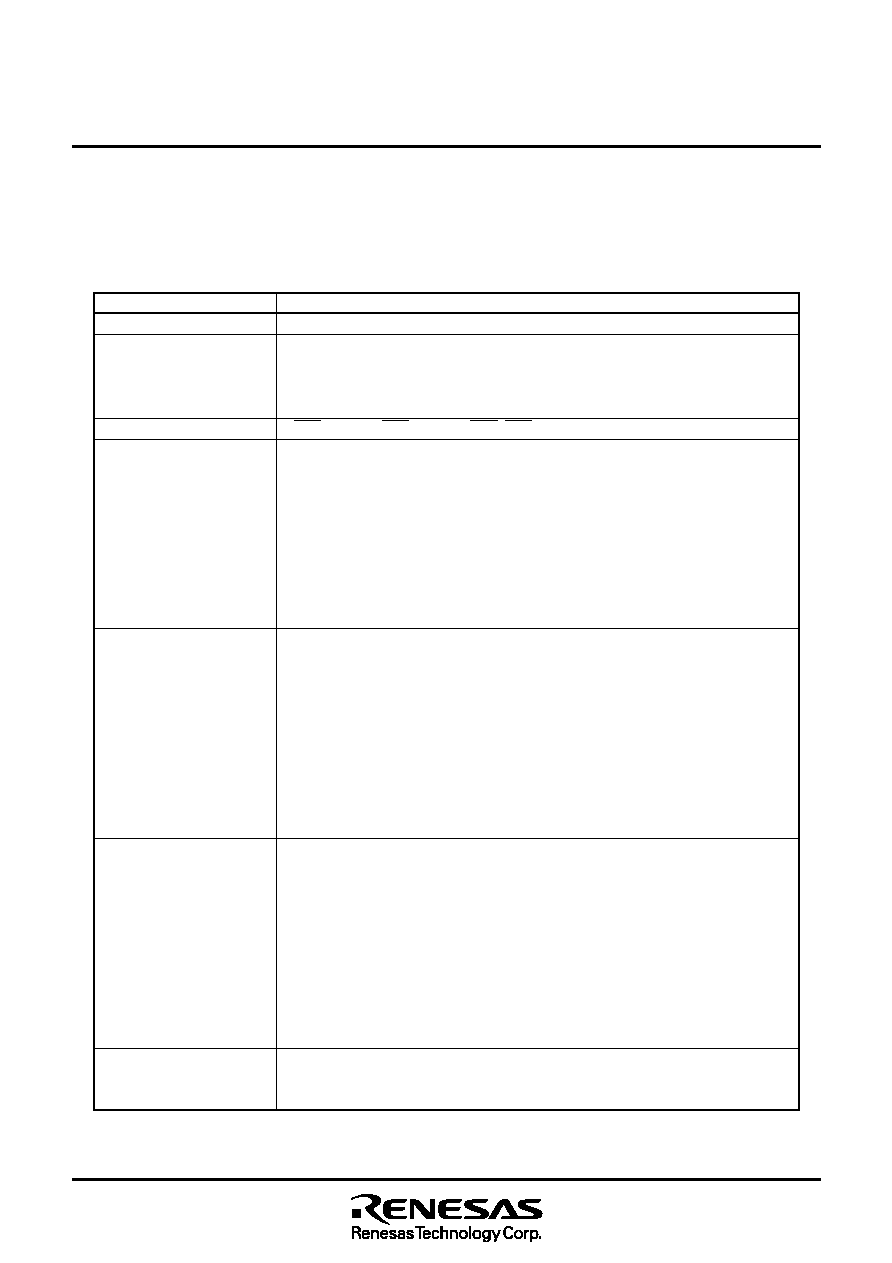

2.11.2 Clock synchronous serial I/O mode

The clock synchronous serial I/O mode uses a transfer clock to transmit and receive data. Tables

2.11.2 and 2.11.3 list the specifications of the clock synchronous serial I/O mode. Figur 2.11.10 shows

the UARTi transmit/receive mode register.

Table 2.11.2 Specifications of clock synchronous serial I/O mode (1)

Interrupt request

generation timing

This error occurs when the next data is ready before contents of UARTi

receive buffer register are read out

Note 1: “n” denotes the value 0016 to FF16 that is set to the UART bit rate generator.

Note 2: If an overrun error occurs, the UARTi receive buffer will have the next data written in. Note also

that the UARTi receive interrupt request bit is not set to “1”.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C63455D | 4-BIT, MROM, 4.1 MHz, MICROCONTROLLER, UUC105 |

| S1C63458F0A0100 | MICROCONTROLLER, PQFP144 |

| S1C63466D | 4-BIT, MROM, 4.1 MHz, MICROCONTROLLER, UUC140 |

| S1C63466F | 4-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PQFP144 |

| S1C63567F0A0100 | MICROCONTROLLER, PQFP144 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C63557D04Q000 | 制造商:Seiko Instruments Inc (SII) 功能描述:EPSON MCU 4BIT |

| S1C63567 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63616 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63632 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63653 | 制造商:EPSON 制造商全稱:EPSON 功能描述:CMOS 4-bit Single Chip Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。