- 您現在的位置:買賣IC網 > PDF目錄376330 > S12SPIV2D (Motorola, Inc.) MC9S12DT128 Device User Guide V02.09 PDF資料下載

參數資料

| 型號: | S12SPIV2D |

| 廠商: | Motorola, Inc. |

| 英文描述: | MC9S12DT128 Device User Guide V02.09 |

| 中文描述: | MC9S12DT128設備的用戶手冊V02.09 |

| 文件頁數: | 126/138頁 |

| 文件大?。?/td> | 2083K |

| 代理商: | S12SPIV2D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁當前第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

MC9S12DT128 Device User Guide — V02.09

126

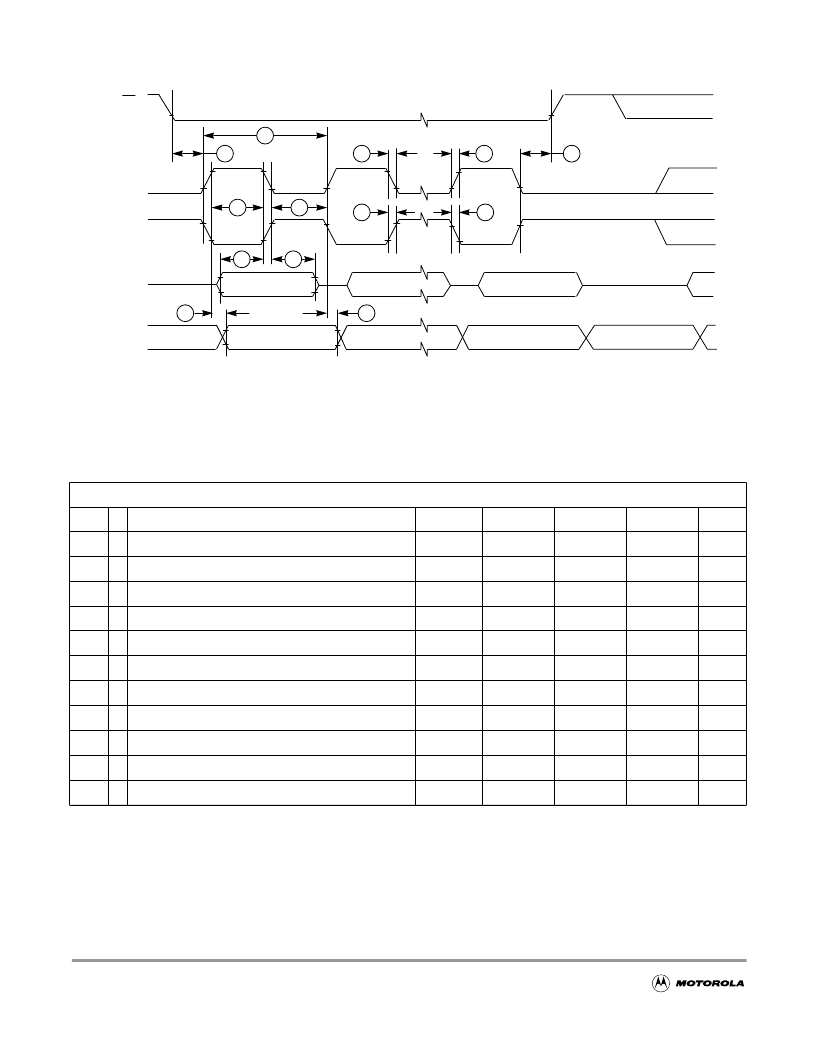

Figure A-6 SPI Master Timing (CPHA =1)

Table A-18 SPI Master Mode Timing Characteristics

1

NOTES

:

1. The numbers 7, 8 in the column labeled “Num” are missing. This has been done on purpose to be consistent between the

Master and the Slave timing shown in

Table A-19

.

Conditions are shown in

Table A-4

unless otherwise noted, C

LOAD

= 200pF on all outputs

Num C

Rating

Symbol

Min

Typ

Max

Unit

1

P Operating Frequency

f

op

DC

1

/

2

f

bus

1

P SCK Period t

sck

= 1./f

op

t

sck

4

2048

t

bus

2

D Enable Lead Time

t

lead

1

/

2

—

t

sck

3

D Enable Lag Time

t

lag

1

/

2

t

sck

4

D Clock (SCK) High or Low Time

t

wsck

t

bus

30

1024 t

bus

ns

5

D Data Setup Time (Inputs)

t

su

25

ns

6

D Data Hold Time (Inputs)

t

hi

0

ns

9

D Data Valid (after SCK Edge)

t

v

25

ns

10

D Data Hold Time (Outputs)

t

ho

0

ns

11

D Rise Time Inputs and Outputs

t

r

25

ns

12

D Fall Time Inputs and Outputs

t

f

25

ns

SCK

(OUTPUT)

SCK

(OUTPUT)

MISO

(INPUT)

MOSI

(OUTPUT)

1

5

6

MSB IN

2

BIT 6 . . . 1

LSB IN

MASTER MSB OUT

2

MASTER LSB OUT

BIT 6 . . . 1

4

4

9

11

12

10

PORT DATA

(CPOL

=

0)

(CPOL

=

1)

PORT DATA

SS

1

(OUTPUT)

2

12

11

3

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

相關PDF資料 |

PDF描述 |

|---|---|

| S12PWM8B8CV1 | MC9S12DT128 Device User Guide V02.09 |

| S12PWM8B8CV1D | MC9S12DT128 Device User Guide V02.09 |

| S12FTS128KV2 | MC9S12DT128 Device User Guide V02.09 |

| S12FTS128KV2D | MC9S12DT128 Device User Guide V02.09 |

| S12MEBIV3 | MC9S12DT128 Device User Guide V02.09 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| S12-SPL | 制造商:Thomas & Betts 功能描述:Universal Recessed Box And Cover |

| S12SPSW | 制造商:Panduit Corp 功能描述:51 RU 1070MM STANDARD SIDE PANEL FOR S-T 制造商:Panduit Corp 功能描述:51 RU 1070mm standard Side Panel for S-t 制造商:Panduit Corp 功能描述:51 RU 1200MM STANDARD SIDE PANEL FOR S-T |

| S12T2.5A-H | 制造商:TE Connectivity 功能描述: |

| S12T2A-H | 制造商:TE Connectivity 功能描述: |

| S12T4H1-A | 制造商:TE Connectivity 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。