- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8150 RTL8150L(M) Specifications PDF資料下載

參數(shù)資料

| 型號: | RTL8150 |

| 英文描述: | RTL8150L(M) Specifications |

| 中文描述: | RTL8150L(米)規(guī)格 |

| 文件頁數(shù): | 15/58頁 |

| 文件大?。?/td> | 616K |

| 代理商: | RTL8150 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

RTL8100B(L)

2001-11-9

Rev.1.41

15

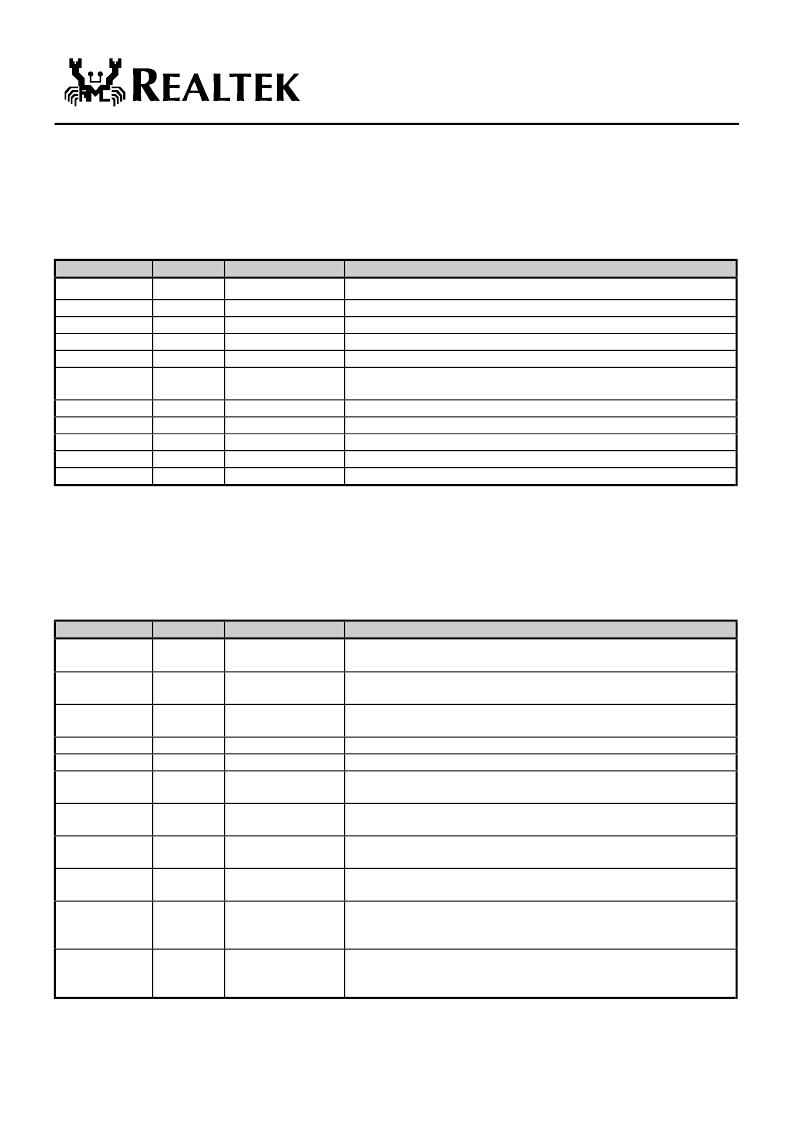

5.5 Interrupt Mask Register

(Offset 003Ch-003Dh, R/W)

This register masks the interrupts that can be generated from the Interrupt Status Register. A hardware reset will clear all mask

bits. Setting a mask bit allows the corresponding bit in the Interrupt Status Register to cause an interrupt. The Interrupt Status

Register bits are always set to 1 if the condition is present, regardless of the state of the corresponding mask bit.

Bit

15

R/W

R/W

Symbol

SERR

Description

System Error Interrupt:

1 => Enable, 0 => Disable.

14

13

12-7

6

5

R/W

R/W

-

R/W

R/W

TimeOut

LenChg

-

FOVW

PUN/LinkChg

Time Out Interrupt:

1 => Enable, 0 => Disable.

Cable Length Change Interrupt:

1 => Enable, 0 => Disable.

Reserved

Rx FIFO Overflow Interrupt:

1 => Enable, 0 => Disable.

Packet Underrun/Link Change Interrupt:

1 => Enable, 0 =>

Disable.

Rx Buffer Overflow Interrupt:

1 => Enable, 0 => Disable.

Transmit Error Interrupt:

1 => Enable, 0 => Disable.

Transmit OK Interrupt:

1 => Enable, 0 => Disable.

Receive Error Interrupt:

1 => Enable, 0 => Disable.

Receive OK Interrupt:

1 => Enable, 0 => Disable.

4

3

2

1

0

R/W

R/W

R/W

R/W

R/W

RXOVW

TER

TOK

RER

ROK

5.6 Interrupt Status Register

(Offset 003Eh-003Fh, R/W)

This register indicates the source of an interrupt when the INTA pin goes active. Enabling the corresponding bits in the Interrupt

Mask Register (IMR) allows bits in this register to produce an interrupt. When an interrupt is active, one of more bits in this

register are set to a “1”. The interrupt Status Register reflects all current pending interrupts, regardless of the state of the

corresponding mask bit in the IMR. Reading the ISR clears all interrupts. Writing to the ISR has no effect.

Bit

15

R/W

R/W

Symbol

SERR

Description

System Error:

Set to 1 when the RTL8100B(L) signals a system error

on the PCI bus.

Time Out:

Set to 1 when the TCTR register reaches to the value of the

TimerInt register.

Cable Length Change:

Cable length is changed after Receiver is

enabled.

Reserved

Rx FIFO Overflow:

Set when an overflow occurs on the Rx status FIFO.

Packet Underrun/Link Change:

Set to 1 when CAPR is written but

Rx buffer is empty, or when link status is changed.

Rx Buffer Overflow:

Set when receive (Rx) buffer ring storage

resources have been exhausted.

Transmit (Tx) Error:

Indicates that a packet transmission was

aborted, due to excessive collisions, according to the TXRR's setting.

Transmit (Tx) OK:

Indicates that a packet transmission is completed

successfully.

Receive (Rx) Error:

Indicates that a packet has either CRC error or

frame alignment error (FAE). The collided frame will not be recognized

as CRC error if the length of this frame is shorter than 16 byte.

Receive (Rx) OK:

In normal mode, indicates the successful completion

the arriving packet exceeds the early Rx threshold.

14

R/W

TimeOut

13

R/W

LenChg

12 - 7

6

5

-

-

R/W

R/W

FOVW

PUN/LinkChg

4

R/W

RXOVW

3

R/W

TER

2

R/W

TOK

1

R/W

RER

0

R/W

ROK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

| RTL8305SB | RTL8305SB |

| RTL8316 | Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8168 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:INTEGRATED GIGABIT ETHERNET CONTROLLER FOR PCI EXPRESS TM |

| RTL8169 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8169 Specification |

| RTL8181 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Wireless LAN Access Point/Gateway Controller |

| RTL8187L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Wireless LAN network interface controller |

| RTL8187L-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Wireless LAN network interface controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。