- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373294 > RM5271-250S 64-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | RM5271-250S |

| 英文描述: | 64-Bit Microprocessor |

| 中文描述: | 64位微處理器 |

| 文件頁(yè)數(shù): | 5/24頁(yè) |

| 文件大小: | 387K |

| 代理商: | RM5271-250S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

Quantum Effect Devices

www.qedinc.com

RM5271 Microprocessor, Document Rev. 1.3

5

System Control Co-processor (CP0)

The system control co-processor, also called co-processor

0 or CP0 in the MIPS architecture, is responsible for the vir-

tual memory sub-system, the exception control system,

and the diagnostics capability of the processor. The

RM5271 CP0 is logically identical to the RM5200.

The memory management unit controls the virtual memory

system page mapping. It consists of an instruction address

translation buffer, ITLB, a data address translation buffer,

DTLB, a Joint instruction and data address translation

buffer, JTLB, and coprocessor registers used by the virtual

memory mapping sub-system.

System Control Co-Processor Register

The RM5271 incorporates all system control coprocessor

(CP0) registers on-chip. These registers provide the path

through which the virtual memory system’s page mapping

is examined and modified, exceptions are handled, and

operating modes are controlled (kernel vs. user mode,

interrupts enabled or disabled, cache features). In addition,

the RM5271 includes registers to implement a real-time

cycle counting facility to aid in cache diagnostic testing and

to assist in data error detection.

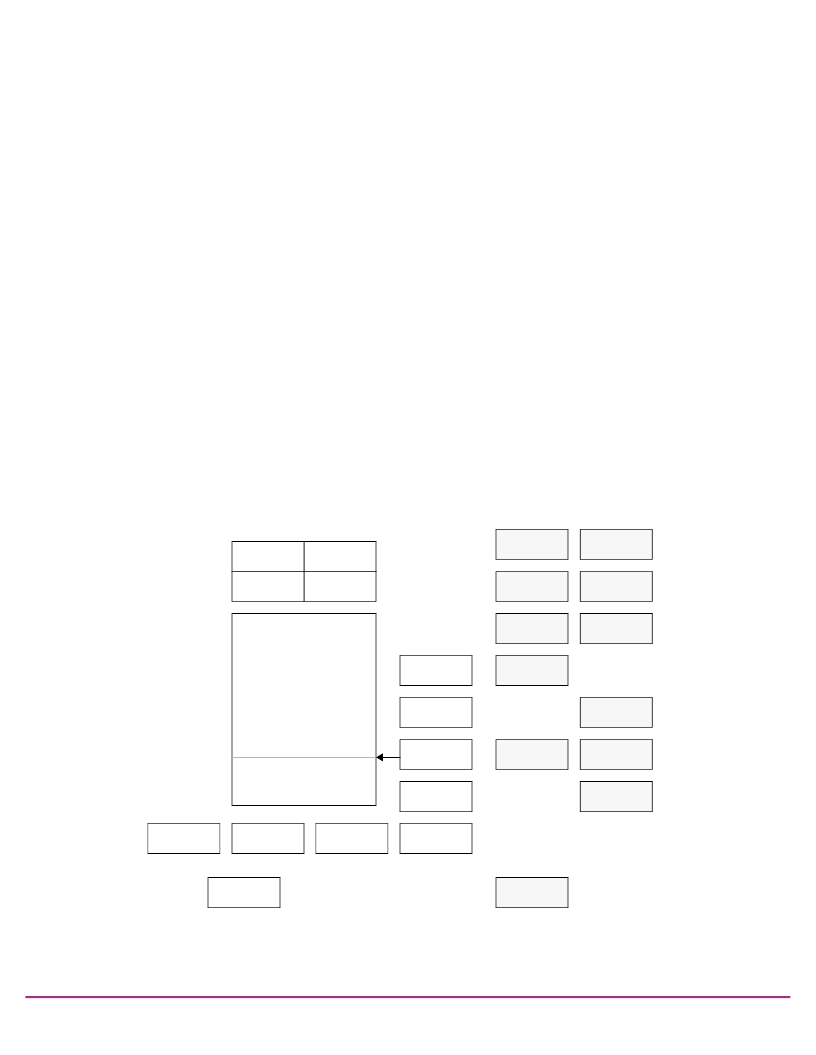

Figure 3 shows the CP0 registers.

Virtual to Physical Address Mapping

The RM5271 provides three modes of virtual addressing:

user mode

kernel mode

supervisor mode

This mechanism is available to system software to provide

a secure environment for user processes. Bits in the CP0

Status register determine which virtual addressing mode is

used. In the user mode, the RM5271 provides a single, uni-

form virtual address space of 256GB (2GB in 32-bit mode).

When operating in the kernel mode, four distinct virtual

address spaces, totalling 1024GB (4GB in 32-bit mode),

are simultaneously available and are differentiated by the

high-order bits of the virtual address.

The RM5271 processors also support a supervisor mode in

which the virtual address space is 256.5GB (2.5GB in 32-

bit mode), divided into three regions based on the high-

order bits of the virtual address.

Figure 4 shows the address space layout for 32-bit opera-

tions.

Figure 3 CP0 Registers

0

47

TLB

(entries protected

from TLBWR)

EntryHi

10*

EntryLo0

2*

EntryLo1

3*

PageMask

5*

Wired

6*

Random

1*

Index

0*

Status

12*

Cause

13*

EPC

14*

ErrorEPC

30*

Count

9*

Compare

11*

Context

4*

PRId

15*

Config

16*

TagHi

29*

TagLo

28*

ECC

26*

CacheErr

27*

BadVAddr

8*

LLAddr

17*

* Register number

XContext

20*

Used for memory

management

Used for exception

processing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM5271-266S | 64-Bit Microprocessor |

| RM5534T | Voltage-Feedback Operational Amplifier |

| RC5534AD | Voltage-Feedback Operational Amplifier |

| RC5534D | Voltage-Feedback Operational Amplifier |

| RC5534N | Voltage-Feedback Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM5271-266S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-300S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-350S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM528-R2 | 制造商:Black Box Corporation 功能描述:Panhead Screws, 10-32, 5/8", , 20-Pack |

| RM52LH3324-048 | 制造商:Esna Technologies 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。