- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296940 > QL4058-3PQN208M (QUICKLOGIC CORP) FPGA, 1008 CLBS, 131328 GATES, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | QL4058-3PQN208M |

| 廠商: | QUICKLOGIC CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 1008 CLBS, 131328 GATES, PQFP208 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, LEAD FREE, PLASTIC, MO-136, QFP-208 |

| 文件頁數(shù): | 43/45頁 |

| 文件大小: | 1332K |

| 代理商: | QL4058-3PQN208M |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁

2007 QuickLogic Corporation

QuickRAM Family Data Sheet Rev. M

7

Figure 5: Loads used for t

PXZ

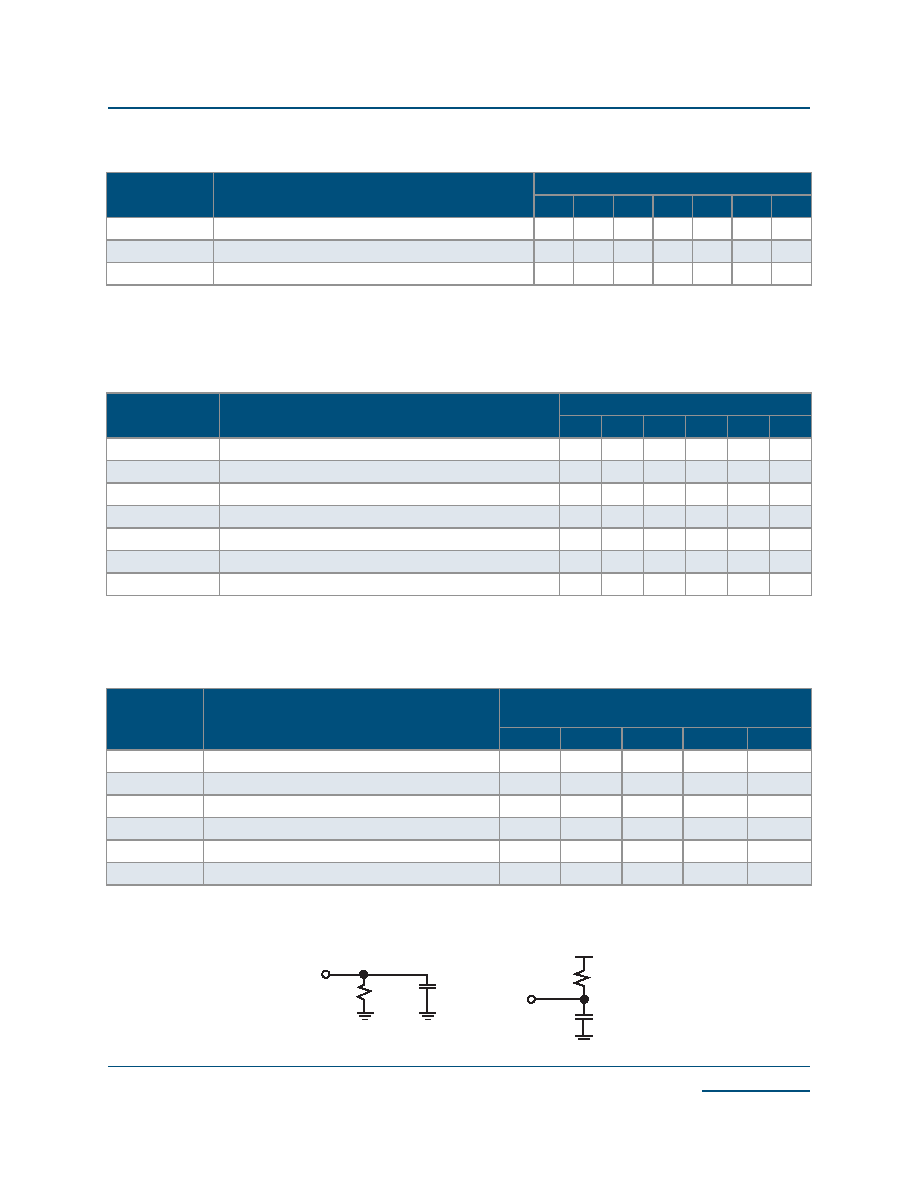

Table 8: Clock Cells

Symbol

Parameter

Propagation Delays (ns) Fanouta

a. The array distributed networks consist of 40 half columns and the global distributed networks consist of 44 half columns, each driven

by an independent buffer. The number of half columns used does not affect clock buffer delay. The array clock has up to 8 loads per

half column. The global clock has up to 11 loads per half column.

1

2

3

4

8

10

11

t

ACK

Array Clock Delay

1.2

1.3

1.5

1.6

1.7

t

GCKP

Global Clock Pin Delay

0.7

t

GCKB

Global Clock Buffer Delay

0.8

0.90.9

1.11.2

1.3

Table 9: I/O Cell Input Delays

Symbol

Parameter

Propagation Delays (ns) Fanouta

a. Stated timing for worst case Propagation Delay over process variation at V

CC = 3.3 V and TA = 25°C. Multiply by the appropriate

Delay Factor, K, for speed grade, voltage and temperature settings as specified in the Operating Range.

1

2

3

4

8

10

t

I/O

Input Delay (bidirectional pad)

1.3

1.6

1.8

2.1

3.1

3.6

t

ISU

Input Register Set-Up Time

3.1

t

IH

Input Register Hold Time

0.0

t

IOCLK

Input Register Clock to Q

0.7

1.0

1.2

1.5

2.5

3.0

t

IORST

Input Register Reset Delay

0.6

0.9

1.1

1.4

2.4

2.9

t

IESU

Input Register Clock Enable Set-Up Time

2.3

t

IEH

Input Register Clock Enable Hold Time

0.0

Table 10: I/O Cell Output Delays

Symbol

Parameter

Propagation Delays (ns)

Output Load Capacitance (pF)

3

50

75

100

150

t

OUTLH

Output Delay Low to High

2.1

2.5

3.1

3.6

4.7

t

OUTHL

Output Delay High to Low

2.2

2.6

3.2

3.7

4.8

t

PZH

Output Delay Tri-state to High

1.2

1.7

2.2

2.8

3.9

t

PZL

Output Delay Tri-state to Low

1.6

2.0

2.6

3.1

4.2

t

PHZ

Output Delay High to Tri-statea

a. The loads presented in

Figure 5 are used for t

PXZ:

2.0

-

t

PLZ

Output Delay High to Tri-statea

1.2

-

1K Ω

t

5pF

PHZ

PLZ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL4058-4PBN456C | FPGA, 1008 CLBS, 131328 GATES, PBGA456 |

| QL4058-4PBN456I | FPGA, 1008 CLBS, 131328 GATES, PBGA456 |

| QL4058-4PBN456M | FPGA, 1008 CLBS, 131328 GATES, PBGA456 |

| QL4058-4PQN208C | FPGA, 1008 CLBS, 131328 GATES, PQFP208 |

| QL4058-4PQN208I | FPGA, 1008 CLBS, 131328 GATES, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL4058-4PB456C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:58,000 Usable PLD Gate QuickRAM ESP Combining Performance, Density and Embedded RAM |

| QL4058-4PB456I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| QL4058-4PB456M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:58,000 Usable PLD Gate QuickRAM ESP Combining Performance, Density and Embedded RAM |

| QL4058-4PQ208C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:58,000 Usable PLD Gate QuickRAM ESP Combining Performance, Density and Embedded RAM |

| QL4058-4PQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:58,000 Usable PLD Gate QuickRAM ESP Combining Performance, Density and Embedded RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。