- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69257 > PTPS659109A1RSL (TEXAS INSTRUMENTS INC) POWER SUPPLY SUPPORT CKT, PQCC48 PDF資料下載

參數(shù)資料

| 型號: | PTPS659109A1RSL |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | POWER SUPPLY SUPPORT CKT, PQCC48 |

| 封裝: | 6 X 6 MM, 1 MM HEIGHT, GREEN, PLASTIC,VQFN-48 |

| 文件頁數(shù): | 81/89頁 |

| 文件大小: | 941K |

| 代理商: | PTPS659109A1RSL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

PRODUCTPREVIEW

SWCS046C – MARCH 2010 – REVISED JUNE 2010

www.ti.com

Bits

Field Name

Description

Type

Reset

1

VMBHI_IT_MSK

VBAT > VMBHI event interrupt mask.

RW

1

When 0, enable the device automatic switch on at BACKUP to OFF or

NOSUPPLY to OFF device state transition (EEPROM bit)

0

VMBDCH_IT_MSK

Setting supply state control though EN3 signal

RW

0

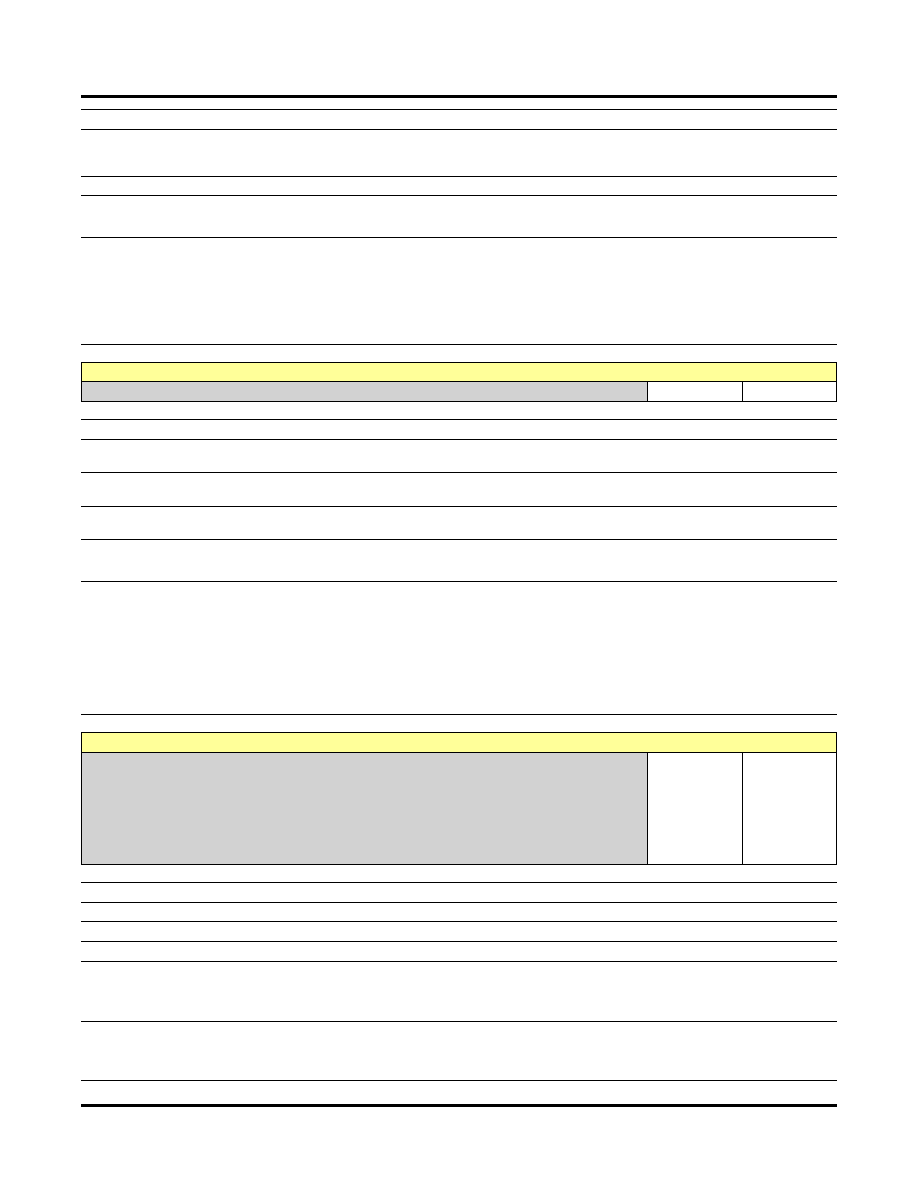

Table 75. INT_STS2_REG

Address Offset

0x52

Physical Address

Instance

Description

Interrupt status register:

The interrupt status bit is set to 1 when the associated interrupt event is detected. Interrupt status bit is

cleared by writing 1.

Type

RW

7

6

5

4

3

2

1

0

Reserved

GPIO0_F_IT

GPIO0_R_IT

Bits

Field Name

Description

Type

Reset

7:2

Reserved

Reserved bit

RW

0

W1 to Clr

1

GPIO0_F_IT

GPIO0 falling edge detection interrupt status

RW

0

W1 to Clr

0

GPIO0_R_IT

GPIO0 rising edge detection interrupt status

RW

0

W1 to Clr

Table 76. INT_MSK2_REG

Address Offset

0x53

Physical Address

Instance

Description

Interrupt mask register:

When *_IT_MSK is set to 1, the associated interrupt is masked: INT1 signal is not activated, but *_IT

interrupt status bit is updated.

When *_IT_MSK is set to 0, the associated interrupt is enabled: INT1 signal is activated, *_IT is

updated.

Type

RW

7

6

5

4

3

2

1

0

Reserved

GPIO0_F_IT_MSK

GPIO0_R_IT_MSK

Bits

Field Name

Description

Type

Reset

7:2

Reserved

Reserved bit

RW

0

1

GPIO0_F_IT_MSK

GPIO_CKSYNC falling edge detection interrupt mask.

RW

0

GPIO0_R_IT_MSK

GPIO_CKSYNC rising edge detection interrupt mask.

RW

0

Table 77. GPIO0_REG

Address Offset

0x60

Physical Address

Instance

Description

GPIO0 configuration register

82

Copyright 2010, Texas Instruments Incorporated

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PTPS659104A1RSL | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659105A1RSL | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS65910A1RSL | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659106A1RSLR | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659102A1RSLR | POWER SUPPLY SUPPORT CKT, PQCC48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PTPS6591102A2ZRCR | 制造商:TI 功能描述:TPS65911 |

| PTPS6591102ZRC | 制造商:TI 功能描述:TPS65911 |

| PTPS6591104A2ZRCR | 制造商:TI 功能描述:TPS65911 |

| PTPS659110A2ZRC | 制造商:TI 功能描述:TPS65911 |

| PTPS659110A2ZRCR | 制造商:TI 功能描述:TPS65911 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。