- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69255 > PTH03060YAS (TEXAS INSTRUMENTS INC) 1-OUTPUT DC-DC REG PWR SUPPLY MODULE PDF資料下載

參數(shù)資料

| 型號: | PTH03060YAS |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源模塊 |

| 英文描述: | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| 封裝: | DIP-10 |

| 文件頁數(shù): | 14/19頁 |

| 文件大小: | 823K |

| 代理商: | PTH03060YAS |

www.ti.com

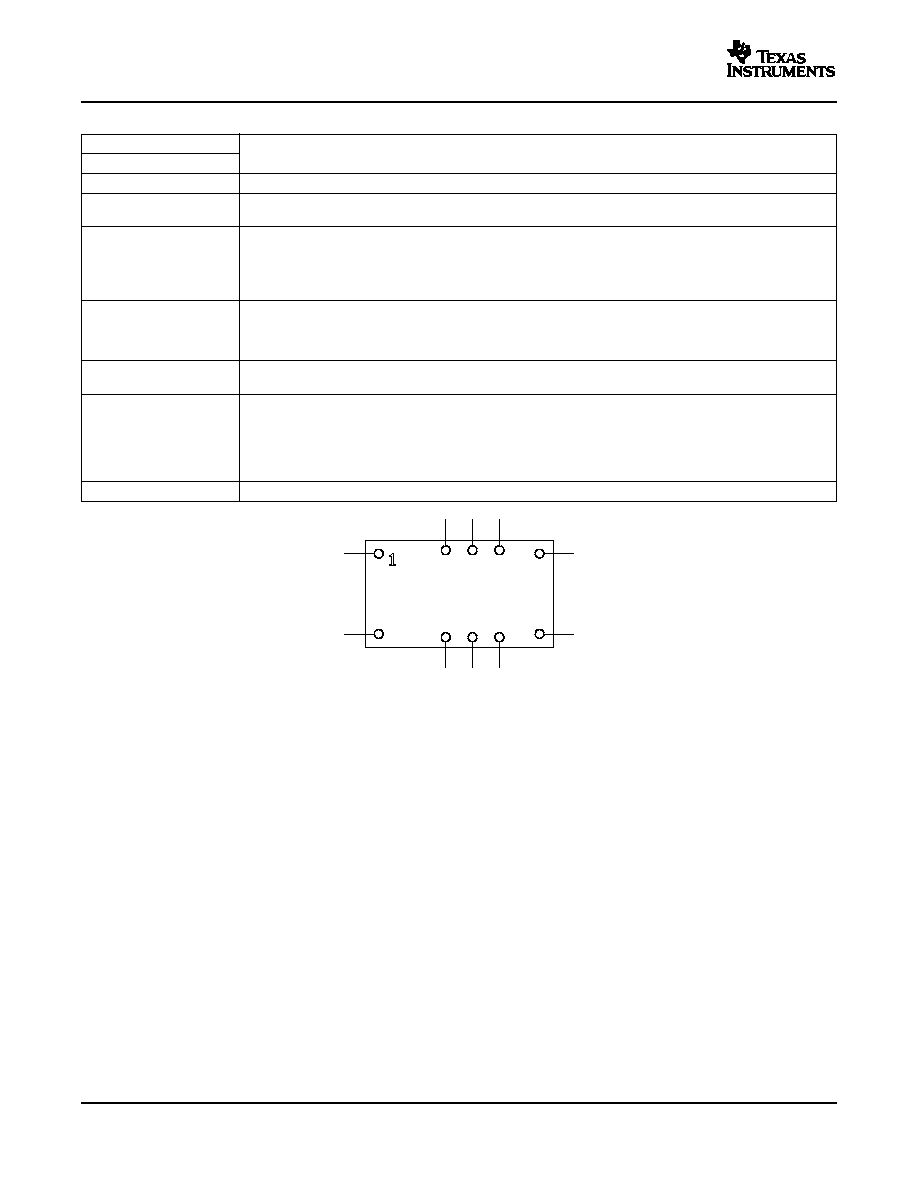

PTHXX060

(Top View)

1

2

10 9

8

7

6

5

4

3

PTH03060Y

PTH05060Y, PTH12060Y

SLTS222A–MARCH 2004–REVISED OCTOBER 2005

Terminal Functions

TERMINAL

DESCRIPTION

NAME

NO.

VIN

2

The positive input voltage power node to the module, which is referenced to common GND.

This is the common ground connection for the VIN and VTT power connections. It is also the 0-VDC reference

GND

1, 7

for the control inputs.

The module senses the voltage at this input to regulate the output voltage, VTT. The voltage at VREF is also

the reference voltage for the system bus receiver comparators. It is normally set to precisely half the bus

VREF

8

driver supply voltage (VDDQ÷ 2), using a resistor divider. The Thevenin impedance of the network driving the

VREF pin should not exceed 500 . See the Typical DDR Application Diagram in the Application Information

section for reference.

This is the regulated power output from the module with respect to the GND node, and the tracking

termination supply for the application data and address buses. It is precisely regulated to the voltage applied

VTT

6

to the module's VREF input, and is active active about 20 ms after a valid input source is applied to the

module. Once active it will track the voltage applied at VREF.

The sense input allows the regulation circuit to compensate for voltage drop between the module and the

Vo Sense

5

load. For optimal voltage accuracy Vo Sense should be connected to VTT.

The Inhibit pin is an open-collector/drain negative logic input that is referenced to GND. Applying a low-level

ground signal to this input turns off the output voltage, VTT. Although the module is inhibited, a voltage, VDDQ

will be present at the output terminals, fed through the DDR memory. When the Inhibit is active, the input

Inhibit

3

current drawn by the regulator is significantly reduced. If the Inhibit pin is left open circuit, the module will

produce an output whenever a valid input source is applied. See the Typical DDR Application Diagram in the

Application Information section for reference.

N/C

4, 9, 10

No connect

4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PTMA402050A1AD | 1-OUTPUT 10 W DC-DC REG PWR SUPPLY MODULE |

| PTMA401120N1AZ | 1-OUTPUT 10 W DC-DC REG PWR SUPPLY MODULE |

| PTMA401120A3AS | 1-OUTPUT 10 W DC-DC REG PWR SUPPLY MODULE |

| PTMA401120P1AST | 1-OUTPUT 10 W DC-DC REG PWR SUPPLY MODULE |

| PTMA403033N2AZT | 1-OUTPUT 10 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PTH03060YAST | 功能描述:DC/DC轉(zhuǎn)換器 10A 3.3V-In Bus Term Pwr Mdl for DDR/QDR RoHS:否 制造商:Murata 產(chǎn)品: 輸出功率: 輸入電壓范圍:3.6 V to 5.5 V 輸入電壓(標稱): 輸出端數(shù)量:1 輸出電壓(通道 1):3.3 V 輸出電流(通道 1):600 mA 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風格:SMD/SMT 封裝 / 箱體尺寸: |

| PTH03060YAZ | 功能描述:DC/DC轉(zhuǎn)換器 10A 3.3V-In Bus Term Pwr Mdl for DDR/QDR RoHS:否 制造商:Murata 產(chǎn)品: 輸出功率: 輸入電壓范圍:3.6 V to 5.5 V 輸入電壓(標稱): 輸出端數(shù)量:1 輸出電壓(通道 1):3.3 V 輸出電流(通道 1):600 mA 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風格:SMD/SMT 封裝 / 箱體尺寸: |

| PTH03060YAZT | 功能描述:DC/DC轉(zhuǎn)換器 10A 3.3V-In Bus Term Pwr Mdl for DDR/QDR RoHS:否 制造商:Murata 產(chǎn)品: 輸出功率: 輸入電壓范圍:3.6 V to 5.5 V 輸入電壓(標稱): 輸出端數(shù)量:1 輸出電壓(通道 1):3.3 V 輸出電流(通道 1):600 mA 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風格:SMD/SMT 封裝 / 箱體尺寸: |

| PTH03060YBH | 制造商:Texas Instruments 功能描述: |

| PTH04000W | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-A, 3.3/5-V INPUT, ADJUSTABLE SWITCHING REGULATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。