- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376279 > PSD8543V15JIT (意法半導(dǎo)體) 3.3V, 8-Bit to 4-Bit, Mux/DeMux Fast Ethernet LAN Switch (Single Enable) w/LED Switching PDF資料下載

參數(shù)資料

| 型號: | PSD8543V15JIT |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 3.3V, 8-Bit to 4-Bit, Mux/DeMux Fast Ethernet LAN Switch (Single Enable) w/LED Switching |

| 中文描述: | Flash在系統(tǒng)可編程ISP的外設(shè)的8位微控制器 |

| 文件頁數(shù): | 86/110頁 |

| 文件大小: | 1737K |

| 代理商: | PSD8543V15JIT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁當(dāng)前第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

86/110

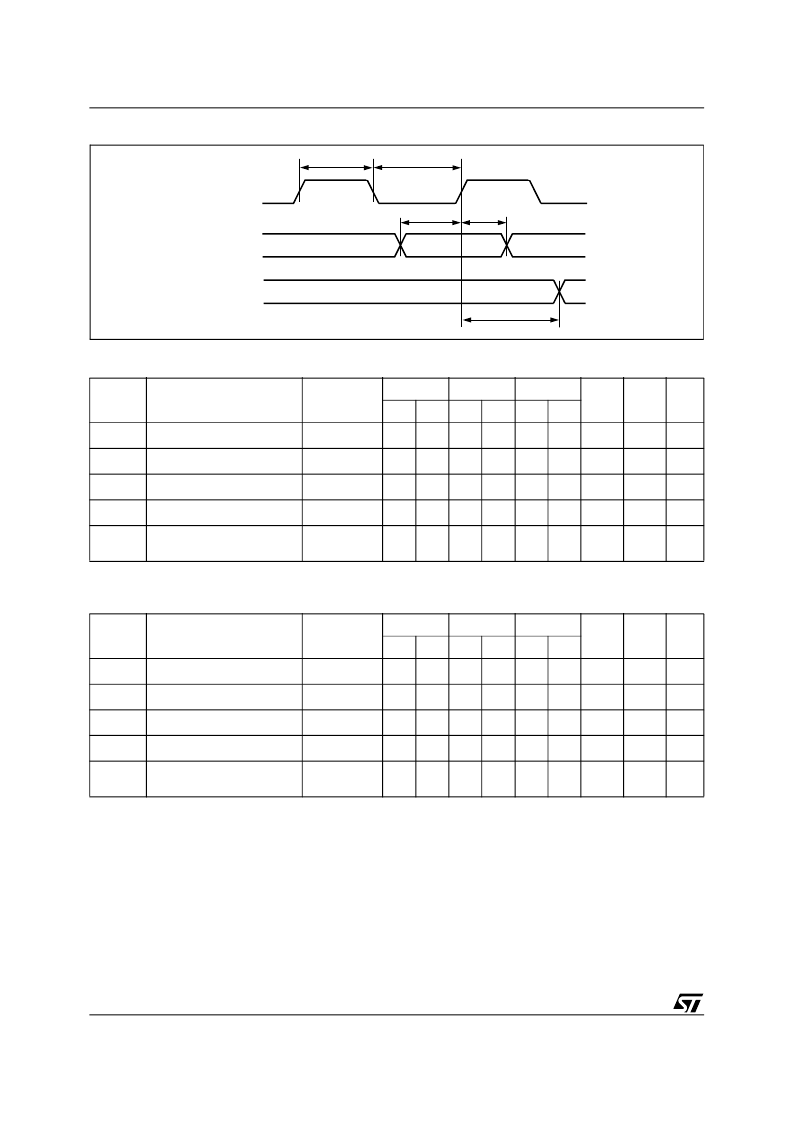

Figure 44. Input Macrocell Timing (product term clock)

Table 53. Input Macrocell Timing (5V devices)

Note: 1. Inputs from Port A, B, and C relative to register/ latch clock from the PLD. ALE/AS latch timings refer to t

AVLX

and t

LXAX

.

Table 54. Input Macrocell Timing (3V devices)

Note: 1. Inputs from Port A, B, and C relative to register/latch clock from the PLD. ALE latch timings refer to t

AVLX

and t

LXAX

.

Symbol

Parameter

Conditions

-70

-90

-15

PT

Aloc

Turbo

Off

Unit

Min

Max

Min

Max

Min

Max

t

IS

Input Setup Time

(Note

1

)

0

0

0

ns

t

IH

Input Hold Time

(Note

1

)

15

20

26

+ 10

ns

t

INH

NIB Input High Time

(Note

1

)

9

12

18

ns

t

INL

NIB Input Low Time

(Note

1

)

9

12

18

ns

t

INO

NIB Input to Combinatorial

Delay

(Note

1

)

34

46

59

+ 2

+ 10

ns

Symbol

Parameter

Conditions

-12

-15

-20

PT

Aloc

Turbo

Off

Unit

Min

Max

Min

Max

Min

Max

t

IS

Input Setup Time

(Note

1

)

0

0

0

ns

t

IH

Input Hold Time

(Note

1

)

25

25

30

+ 20

ns

t

INH

NIB Input High Time

(Note

1

)

12

13

15

ns

t

INL

NIB Input Low Time

(Note

1

)

12

13

15

ns

t

INO

NIB Input to Combinatorial

Delay

(Note

1

)

46

62

70

+ 4

+ 20

ns

t

INH

t

INL

t

INO

t

IH

t

IS

PT CLOCK

INPUT

OUTPUT

AI03101

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD9543V15JIT | 3.3V, Wide Bandwidth, 2-Channel, 2:1 Mux/Demux USB 2.0 Switch |

| PSD8134V15JIT | Dual SPDT for USB 2.0 HS Compliance and Flow through Pinout |

| PSD9134V15JIT | Dual SPDT for USB 2.0 HS Compliance with 8kV ESD Protection |

| PSD8334V15JIT | Dual SPDT for USB 2.0 HS Compliance with Charge-pump |

| PSD9334V15JIT | 3.3V, 2-Channel, 4:1 Mux USB 2.0 Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD854F2-15J | 制造商:STMicroelectronics 功能描述:4556DIE2HR - Trays |

| PSD854F2-70J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2-70M | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2-90J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2-90JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。