- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368236 > PSD835F1V-B-20B81 (意法半導(dǎo)體) Configurable Memory System on a Chip for 8-Bit Microcontrollers PDF資料下載

參數(shù)資料

| 型號(hào): | PSD835F1V-B-20B81 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| 中文描述: | 在8片位微控制器可配置存儲(chǔ)系統(tǒng) |

| 文件頁數(shù): | 24/110頁 |

| 文件大小: | 570K |

| 代理商: | PSD835F1V-B-20B81 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

PSD835G2

PSD8XX Family

23

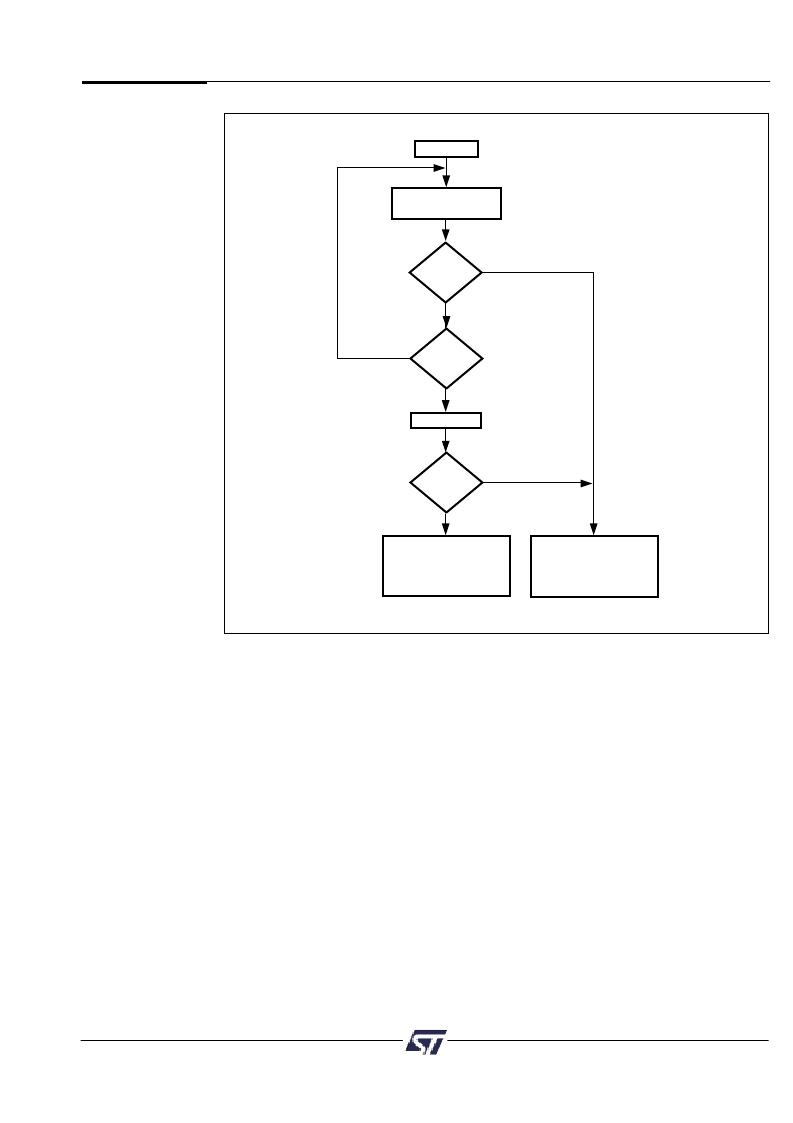

Figure 4. Data Polling Flow Chart

START

READ DQ5 & DQ7

at VALID ADDRESS

YES

YES

YES

NO

NO

NO

=

DATA7

DQ5

=1

=

DATA

READ DQ7

FAIL

Program/Erase

Operation Failed

Issue Reset Instruction

PASS

Program/Erase

Operation is

Completed

The

PSD835G2

Functional

Blocks

(cont.)

9.1.1.7.2 Data Toggle

Checking the Data Toggle bit on DQ6 is a method of determining whether a Program or

Erase instruction is in progress or has completed. Figure 5 shows the Data Toggle

algorithm.

When the MCU issues a programming instruction, the embedded algorithm within the

PSD835G2 begins. The MCU then reads the location to be programmed in Flash to check

status. Data bit DQ6 of this location will toggle each time the MCU reads this location until

the embedded algorithm is complete. The MCU continues to read this location, checking

DQ6 and monitoring the Error bit on DQ5. When DQ6 stops toggling (two consecutive

reads yield the same value), and the Error bit on DQ5 remains

‘

0

’

, then the embedded

algorithm is complete. If the Error bit on DQ5 is

‘

1

’

, the MCU should test DQ6 again, since

DQ6 may have changed simultaneously with DQ5 (see Figure 5).

The Error bit at DQ5 will be set if either an internal timeout occurred while the embedded

algorithm attempted to program, or if the MCU attempted to program a

‘

1

’

to a bit that was

not erased (not erased is logic

‘

0

’

).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD835F1V-B-20B81I | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD835F1V-B-20J | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD835F1V-B-20JI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD835F1V-B-20M | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD835F1V-B-20MI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD835G2-70U | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 5.0V 4M 70ns RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2-90U | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 5.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2-90UI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 5.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2V-12UI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 3.0V 4M 120ns RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| PSD835G2V-90U | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 3.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。