- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378055 > PM5392 (PMC-Sierra, Inc.) SATURN User Network Interface for 9.953 Gbit/s PDF資料下載

參數(shù)資料

| 型號: | PM5392 |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | SATURN User Network Interface for 9.953 Gbit/s |

| 中文描述: | 土星用戶網(wǎng)絡(luò)接口/為9.953千兆? |

| 文件頁數(shù): | 1/2頁 |

| 文件大小: | 41K |

| 代理商: | PM5392 |

PM5392

Advance

SATURN User Network Interface for 9.953 Gbit/s

S/UNI-9953-POS

PMC-2010908 (A1)

PROPRIETARY AND CONFIDENTIAL TO PMC

-

SIERRA, INC., AND FOR ITS CUSTOMERS

’

INTERNAL USE

Copyright PMC

-

Sierra, Inc. 2001

GENERAL DESCRIPTION

The S/UNI-9953-POS is a single chip

ATM, POS User-Network Interface

operating at 9953.28 Mbit/s. The S/UNI

9953-POS is intended for use in OC-

192c and high-density OC-48c

POS/ATM applications.

FEATURES

Supports framing, scrambling/

descrambling and pointer processing

for the following:

STS-192c (STM-64-64c).

4 x STS-48c (4 x STM-16-16c).

STS-192 (STM-64) channelized

down to STS-48c (STM-16c).

Supports alarm signal

insertion/detection, B1/2/3 processing

and insertion/termination of SONET

Section/Line/Path overhead bytes (or

SDH equivalents).

Provides ATM and POS payload

processing for:

STS-192c (STM-64-64c)

4 x STS-48c (4 x STM-16-16c).

STS-192 (STM-64) channelized

down to STS-48c (STM-16c).

INTERFACES

Provides SATURN

POS-PHY

Level 4 16-bit LVDS System-side

Interface (clocked at 700 MHz

nominal).

Directly connects to optics via 16 bit by

622 MHz OIF SFI-4 (OIF99.102) line-

side interface.

POS/ATM

Implements the ATM Forum User

Network Interface Specification and

the ATM physical layer for Broadband

ISDN according to CCITT

Recommendation I.432.

Implements the Point-to-Point Protocol

(PPP) over SONET/SDH specification

according to RFC 2615(1619)/1662 of

the PPP Working Group of the Internet

Engineering Task Force (IETF).

GENERAL

Provides internal FIFOs (16 KB

ingress, 20 KB egress) to

accommodate system latencies.

Provides line-side and system-side

loopbacks for system level diagnostic

capability.

Provides support for automatic

protection switching (APS) via two 16-

bit LVDS 777.76 MHz ports.

Provides a generic 16-bit

microprocessor bus interface for

configuration, control and status

monitoring.

Standard 5 signal P1149.1 JTAG test

port.

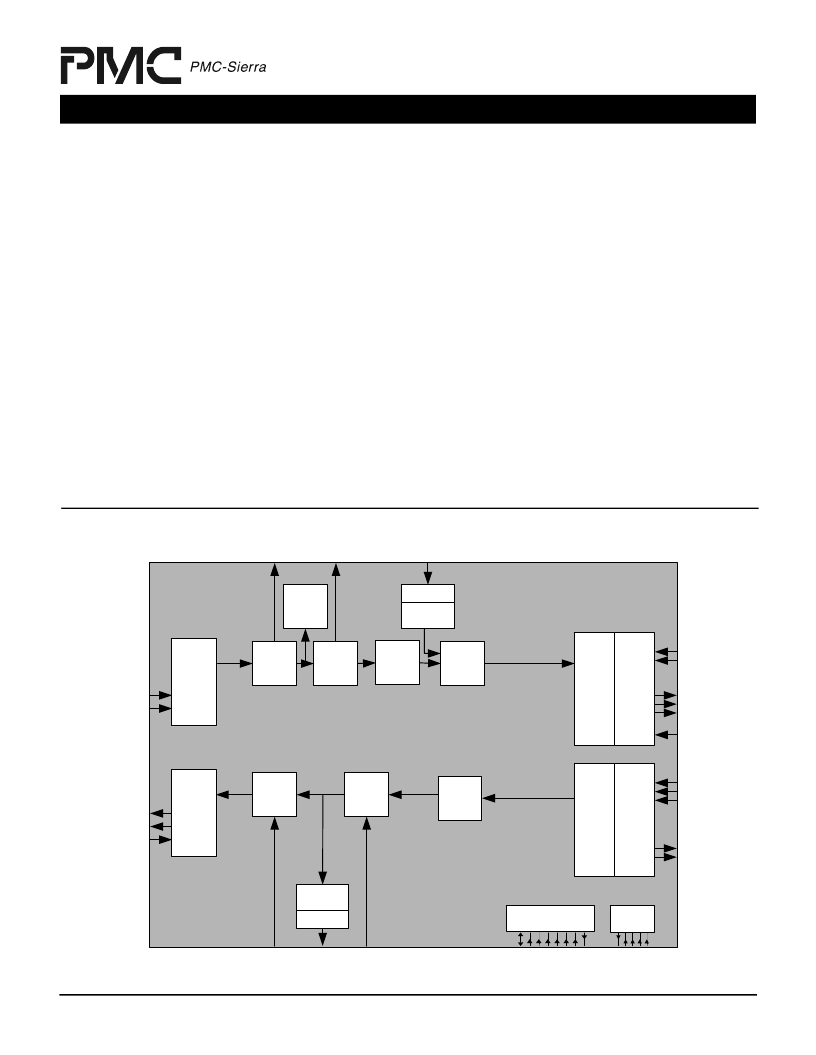

Rx

Transport

O/H

Processor

APS

Rx Path

O/H

Processor

Rx Payload

Aligner

Rx Cell/

Frame

Processor

Rx SONET

BER

Monitor

Tx

Transport

O/H

Processor

Tx High-

Order Path

O/H

Processor

APS

LVDS I/F

TXCLK_SRC+/-

RXCLK+/-

RXDATA+/-

TXDATA +/-

TXCLK+/-

R

R

T

T

O

I

T

T

T

T

T

Microprocessor

JTAG

D

C

A

A

W

R

I

R

POS-PHY

Level 4

Interface

Ingress

Flexible

FIFO

POS-PHY

Level 4

Interface

Egress

Flexible

FIFO

PL4 REF +/-

RDCLK +/-

RDAT+/-

RSCLK

RSTAT

TDCLK +/-

TDAT+/-

TCTL+/-

TSCLK

TSTAT

RCTL+/-

SFI-4

Rx

Interface

SFI-4

Tx

Interface

LVDS I/F

Tx Cell/

Frame

Processor

BLOCK DIAGRAM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM5945-UTP5 | ATM PHYSICAL INTERFACE APPLICATION BOARD FOR CAT-5 UTP |

| PM5945 | CONN |

| PM6341 | E1 TRANSCEIVER |

| PM6341-QI | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM6341-RI | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM5397-FI | 制造商:PMC-Sierra 功能描述:ARROW-2xGE EOL150207 |

| PM5397FIP | 制造商:PMC-Sierra 功能描述: |

| PM53A | 功能描述:鉗型萬用表及配件 AUTOMATIC POCKET DMM W/VOLTECT RoHS:否 制造商:Fluke 準(zhǔn)確性:2 % 測距:400 A |

| PM53-BC | 功能描述:LED面板上的指示器 Panel Mount LED 5mm Red/Green RoHS:否 制造商:Dialight LED 大小:3 mm 照明顏色:Green 透鏡顏色/類型:Diffused 波長:565 nm 正向電流:12 mA 正向電壓:5 V 封裝:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。