- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄368041 > PLCDA03C-6 Direct ProTek Replacement:PLCDA03C-6 PDF資料下載

參數(shù)資料

| 型號(hào): | PLCDA03C-6 |

| 英文描述: | Direct ProTek Replacement:PLCDA03C-6 |

| 中文描述: | 直接太克替代:PLCDA03C - 6 |

| 文件頁(yè)數(shù): | 4/5頁(yè) |

| 文件大小: | 450K |

| 代理商: | PLCDA03C-6 |

4

www.protekdevices.com

05102.R2 1/02

PLCDA03C-6

thru

PLCDA15C-6

APPLICATION NOTE

The PLCDAxxC-6 Series are low capacitance, bidirectional TVS arrays that are designed to protect I/O or high speed data lines from the damaging

effects of ESD or EFT. This product series has a surge capability of 500 Watts P

PP

per line for an 8/20μs waveshape and offers ESD protection >

40kv.

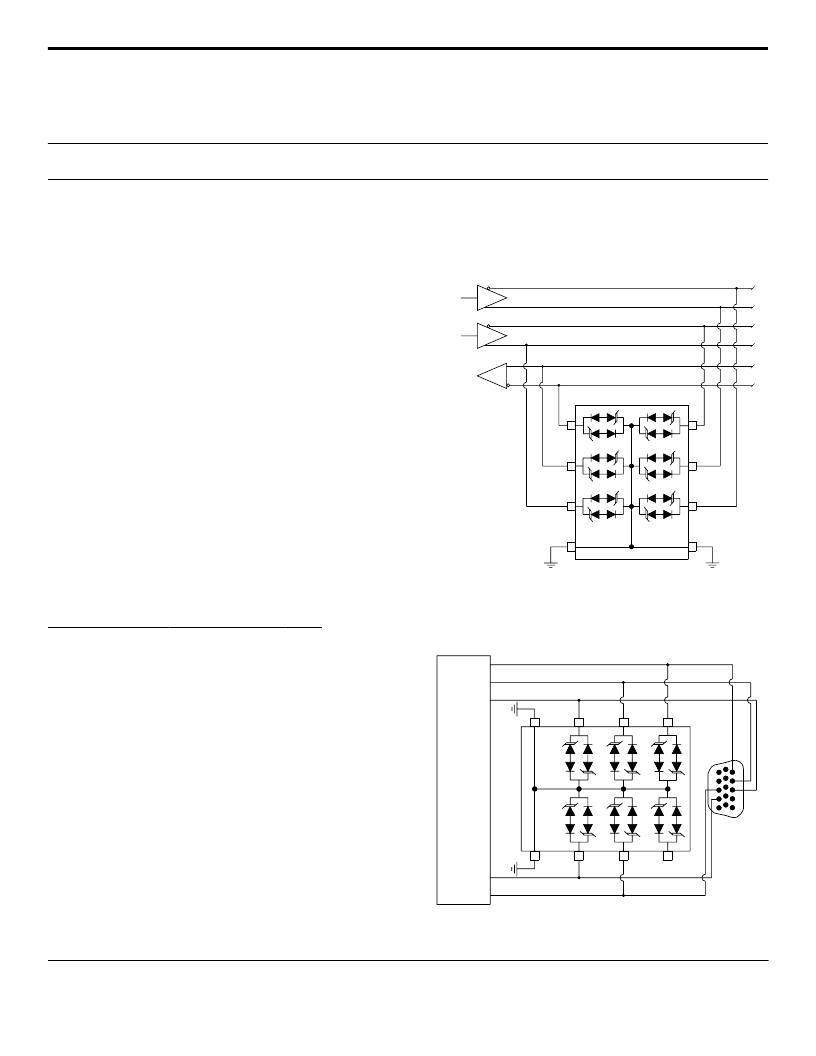

BIDIRECTIONAL COMMON MODE CONFIGURATION (Figure 1)

Ideal for use multimode transceiver I/O lines, the PLCDAxxC-6 Series provides

up to six (6) lines of protection in a common mode configuration as depicted in

Figure 1.

Circuit connectivity is as follows:

Line 1 is connected to Pin 1.

Line 2 is connected to Pin 2.

Line 3 is connected to Pin 3.

Line 4 is connected to Pin 8.

Line 5 is connected to Pin 7.

Line 6 is connected to Pin 6.

Pins 4 and 5 are connected to Ground.

BIDIRECTIONAL COMMON MODE CONFIGURATION (Figure 2)

The PLCDAxxC-6 Series also provides video line applications six (6) lines of

protection in a common mode configuration as depicted in Figure 2.

Circuit connectivity is as follows:

Line 1 (Red) is connected to Pin 1.

Line 2 (Green) is connected to Pin 2.

Line 3 (Blue) is connected to Pin 3.

Line 4 (VSYNC) is connected to Pin 6.

Line 5 (HSYNC) is connected to Pin 7.

Pins 4 and 5 are connected to Ground.

CIRCUIT BOARD LAYOUT RECOMMENDATIONS

Circuit board layout is critical for Electromagnetic Compat-

ibility (EMC) protection. The following guidelines are

recommended:

The protection device should be placed near the input

terminals or connectors, the device will divert the

transient current immediately before it can be coupled

into the nearby traces.

The path length between the TVS device and the

protected line should be minimized.

All conductive loops including power and ground loops

should be minimized.

The transient current return path to ground should be

kept as short as possible to reduce parasitic induc-

tance.

Ground planes should be used whenever possible.

For multilayer PCBs, use ground vias.

1

2

3

4

8

7

6

5

LINE 6

LINE 1

LINE 2

LINE 3

LINE 4

LINE 5

Figure 1: Typical Transceiver Protection Circuit

1

2

3

4

8

7

6

5

LINE 1 (RED)

LINE 2 (GREEN)

LINE 3 (BLUE)

LINE 4 (VSYNC)

LINE 4 (HSYNC)

G

DB-15

CONNECTOR

Figure 2: Typical Video Line Protection Circuit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PLCDA05C-6 | Direct ProTek Replacement:PLCDA05C-6 |

| PLCDA15C-6 | Direct ProTek Replacement:PLCDA15C-6 |

| PLCDA03 | Direct ProTek Replacement:PLCDA03 |

| GBIT03C | Direct ProTek Replacement:PLCDA03 |

| GBIT05C | Direct ProTek Replacement:PLCDA05 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PLCDA03C-6_07 | 制造商:PROTEC 制造商全稱:Protek Devices 功能描述:LOW CAPACITANCE TVS ARRAY |

| PLCDA03C-6_11 | 制造商:PROTEC 制造商全稱:Protek Devices 功能描述:500 WATT MULTI-LINE CAPACITANCE TVS ARRAY |

| PLCDA03C-6_12 | 制造商:PROTEC 制造商全稱:Protek Devices 功能描述:500 WATT MULTI-LINE LOW CAPACITANCE TVS ARRAY |

| PLCDA03C-6-LF | 制造商:ProTek Devices 功能描述:ESD Suppressor TVS 15KV 8-Pin SO Tube 制造商:ProTek Devices 功能描述:PLCDA03C-6 Series 6 Channel 20 Vcl 4.5 Vbr 8 pF Bi-directional TVS Array SOIC-8 |

| PLCDA03C-6-LF-T7 | 制造商:ProTek Devices 功能描述:ESD Suppressor TVS 15KV 8-Pin SO T/R |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。