- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗10890 > PIC16C621T-04/SS (Microchip Technology)IC MCU OTP 1KX14 COMP 20SSOP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | PIC16C621T-04/SS |

| 寤犲晢锛� | Microchip Technology |

| 鏂囦欢闋�(y猫)鏁�(sh霉)锛� | 61/89闋�(y猫) |

| 鏂囦欢澶�?銆�?/td> | 0K |

| 鎻忚堪锛� | IC MCU OTP 1KX14 COMP 20SSOP |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 1,600 |

| 绯诲垪锛� | PIC® 16C |

| 鏍稿績铏曠悊鍣細 | PIC |

| 鑺珨灏哄锛� | 8-浣� |

| 閫熷害锛� | 4MHz |

| 澶栧湇瑷�(sh猫)鍌欙細 | 娆犲妾㈡脯(c猫)/寰�(f霉)浣嶏紝POR锛學DT |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 13 |

| 绋嬪簭瀛樺劜(ch菙)鍣ㄥ閲忥細 | 1.75KB锛�1K x 14锛� |

| 绋嬪簭瀛樺劜(ch菙)鍣ㄩ鍨嬶細 | OTP |

| RAM 瀹归噺锛� | 80 x 8 |

| 闆诲 - 闆绘簮 (Vcc/Vdd)锛� | 3 V ~ 6 V |

| 鎸暕鍣ㄥ瀷锛� | 澶栭儴 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 灏佽/澶栨锛� | 20-SSOP锛�0.209"锛�5.30mm 瀵級 |

| 鍖呰锛� | 甯跺嵎 (TR) |

绗�1闋�(y猫)绗�2闋�(y猫)绗�3闋�(y猫)绗�4闋�(y猫)绗�5闋�(y猫)绗�6闋�(y猫)绗�7闋�(y猫)绗�8闋�(y猫)绗�9闋�(y猫)绗�10闋�(y猫)绗�11闋�(y猫)绗�12闋�(y猫)绗�13闋�(y猫)绗�14闋�(y猫)绗�15闋�(y猫)绗�16闋�(y猫)绗�17闋�(y猫)绗�18闋�(y猫)绗�19闋�(y猫)绗�20闋�(y猫)绗�21闋�(y猫)绗�22闋�(y猫)绗�23闋�(y猫)绗�24闋�(y猫)绗�25闋�(y猫)绗�26闋�(y猫)绗�27闋�(y猫)绗�28闋�(y猫)绗�29闋�(y猫)绗�30闋�(y猫)绗�31闋�(y猫)绗�32闋�(y猫)绗�33闋�(y猫)绗�34闋�(y猫)绗�35闋�(y猫)绗�36闋�(y猫)绗�37闋�(y猫)绗�38闋�(y猫)绗�39闋�(y猫)绗�40闋�(y猫)绗�41闋�(y猫)绗�42闋�(y猫)绗�43闋�(y猫)绗�44闋�(y猫)绗�45闋�(y猫)绗�46闋�(y猫)绗�47闋�(y猫)绗�48闋�(y猫)绗�49闋�(y猫)绗�50闋�(y猫)绗�51闋�(y猫)绗�52闋�(y猫)绗�53闋�(y猫)绗�54闋�(y猫)绗�55闋�(y猫)绗�56闋�(y猫)绗�57闋�(y猫)绗�58闋�(y猫)绗�59闋�(y猫)绗�60闋�(y猫)鐣�(d膩ng)鍓嶇61闋�(y猫)绗�62闋�(y猫)绗�63闋�(y猫)绗�64闋�(y猫)绗�65闋�(y猫)绗�66闋�(y猫)绗�67闋�(y猫)绗�68闋�(y猫)绗�69闋�(y猫)绗�70闋�(y猫)绗�71闋�(y猫)绗�72闋�(y猫)绗�73闋�(y猫)绗�74闋�(y猫)绗�75闋�(y猫)绗�76闋�(y猫)绗�77闋�(y猫)绗�78闋�(y猫)绗�79闋�(y猫)绗�80闋�(y猫)绗�81闋�(y猫)绗�82闋�(y猫)绗�83闋�(y猫)绗�84闋�(y猫)绗�85闋�(y猫)绗�86闋�(y猫)绗�87闋�(y猫)绗�88闋�(y猫)绗�89闋�(y猫)

64

AT90S1200

0838H鈥揂VR鈥�03/02

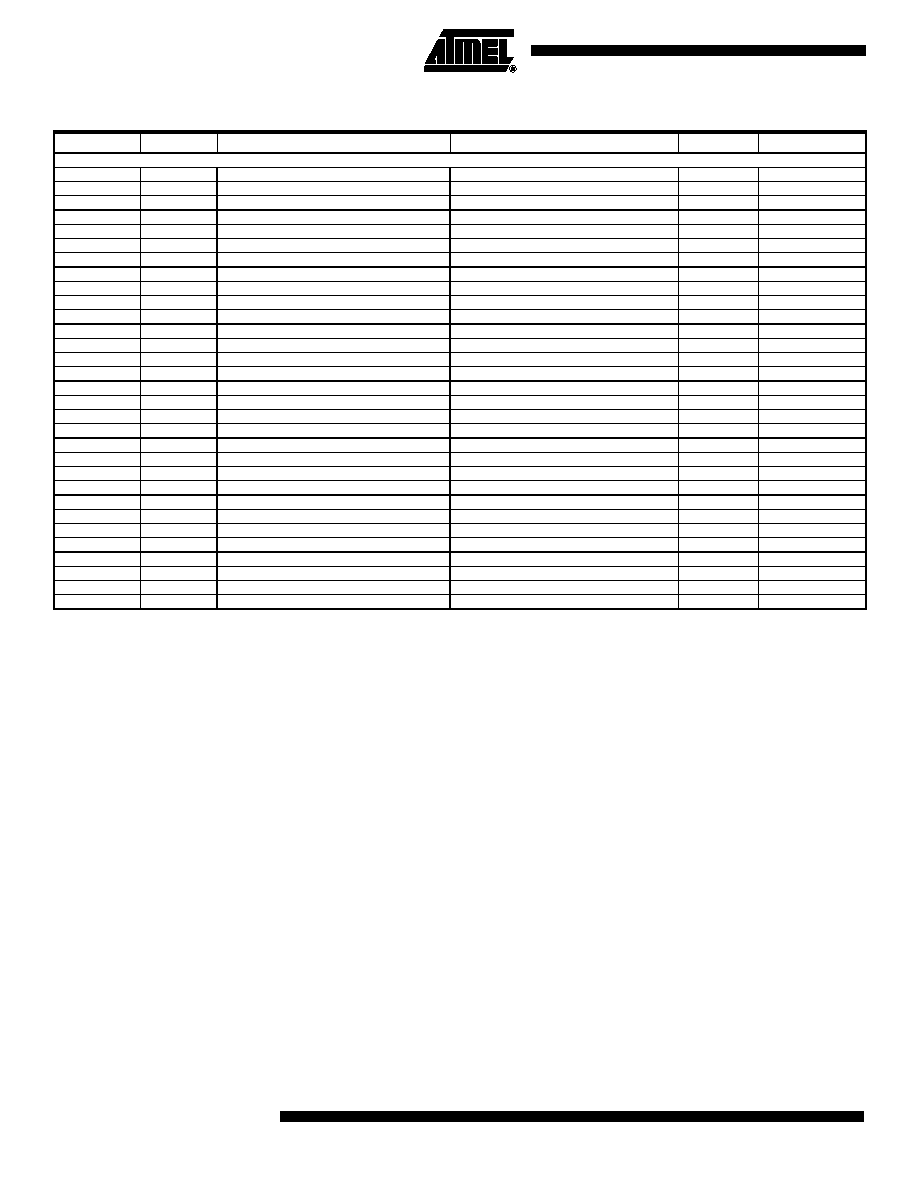

BIT AND BIT-TEST INSTRUCTIONS

SBI

P, b

Set Bit in I/O Register

I/O(P,b)

鈫� 1

None

2

CBI

P, b

Clear Bit in I/O Register

I/O(P,b)

鈫� 0

None

2

LSL

Rd

Logical Shift Left

Rd(n+1)

鈫� Rd(n), Rd(0) 鈫� 0

Z,C,N,V

1

LSR

Rd

Logical Shift Right

Rd(n)

鈫� Rd(n+1), Rd(7) 鈫� 0

Z,C,N,V

1

ROL

Rd

Rotate Left through Carry

Rd(0)

鈫� C,Rd(n+1) 鈫� Rd(n),C 鈫� Rd(7)

Z,C,N,V

1

ROR

Rd

Rotate Right through Carry

Rd(7)

鈫� C,Rd(n) 鈫� Rd(n+1),C 鈫� Rd(0)

Z,C,N,V

1

ASR

Rd

Arithmetic Shift Right

Rd(n)

鈫� Rd(n+1), n = 0..6

Z,C,N,V

1

SWAP

Rd

Swap Nibbles

Rd(3..0)

鈫� Rd(7..4),Rd(7..4) 鈫� Rd(3..0)

None

1

BSET

s

Flag Set

SREG(s)

鈫� 1

SREG(s)

1

BCLR

s

Flag Clear

SREG(s)

鈫� 0

SREG(s)

1

BST

Rr, b

Bit Store from Register to T

T

鈫� Rr(b)

T

1

BLD

Rd, b

Bit Load from T to Register

Rd(b)

鈫� T

None

1

SEC

Set Carry

C

鈫� 1C

1

CLC

Clear Carry

C

鈫� 0C

1

SEN

Set Negative Flag

N

鈫� 1N

1

CLN

Clear Negative Flag

N

鈫� 0N

1

SEZ

Set Zero Flag

Z

鈫� 1Z

1

CLZ

Clear Zero Flag

Z

鈫� 0Z

1

SEI

Global Interrupt Enable

I

鈫� 1I

1

CLI

Global Interrupt Disable

I

鈫� 0I

1

SES

Set Signed Test Flag

S

鈫� 1S

1

CLS

Clear Signed Test Flag

S

鈫� 0S

1

SEV

Set Two鈥檚 Complement Overflow

V

鈫� 1V

1

CLV

Clear Two鈥檚 Complement Overflow

V

鈫� 0V

1

SET

Set T in SREG

T

鈫� 1T

1

CLT

Clear T in SREG

T

鈫� 0T

1

SEH

Set Half-carry Flag in SREG

H

鈫� 1H

1

CLH

Clear Half-carry Flag in SREG

H

鈫� 0H

1

NOP

No Operation

None

1

SLEEP

Sleep

(see specific descr. for Sleep function)

None

1

WDR

Watchdog Reset

(see specific descr. for WDR/timer)

None

1

Instruction Set Summary (Continued)

Mnemonic

Operands

Description

Operation

Flags

# Clocks

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| VE-26F-IX-F2 | CONVERTER MOD DC/DC 72V 75W |

| PIC16C621T-04I/SS | IC MCU OTP 1KX14 COMP 20SSOP |

| PIC16C621T-04E/SS | IC MCU OTP 1KX14 COMP 20SSOP |

| PIC16C621T-04E/SO | IC MCU OTP 1KX14 COMP 18SOIC |

| PIC16C621AT-20/SS | IC MCU OTP 1KX14 COMP 20SSOP |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| PIC16C621T-20/SO | 鍔熻兘鎻忚堪:8浣嶅井鎺у埗鍣� -MCU 1.75KB 80 RAM 13 I/O RoHS:鍚� 鍒堕€犲晢:Silicon Labs 鏍稿績:8051 铏曠悊鍣ㄧ郴鍒�:C8051F39x 鏁�(sh霉)鎿�(j霉)绺界窔瀵害:8 bit 鏈€澶ф檪(sh铆)閻橀牷鐜�:50 MHz 绋嬪簭瀛樺劜(ch菙)鍣ㄥぇ灏�:16 KB 鏁�(sh霉)鎿�(j霉) RAM 澶у皬:1 KB 鐗囦笂 ADC:Yes 宸ヤ綔闆绘簮闆诲:1.8 V to 3.6 V 宸ヤ綔婧害鑼冨湇:- 40 C to + 105 C 灏佽 / 绠遍珨:QFN-20 瀹夎棰�(f膿ng)鏍�:SMD/SMT |

| PIC16C621T-20/SS | 鍔熻兘鎻忚堪:8浣嶅井鎺у埗鍣� -MCU 1.75KB 80 RAM 13 I/O RoHS:鍚� 鍒堕€犲晢:Silicon Labs 鏍稿績:8051 铏曠悊鍣ㄧ郴鍒�:C8051F39x 鏁�(sh霉)鎿�(j霉)绺界窔瀵害:8 bit 鏈€澶ф檪(sh铆)閻橀牷鐜�:50 MHz 绋嬪簭瀛樺劜(ch菙)鍣ㄥぇ灏�:16 KB 鏁�(sh霉)鎿�(j霉) RAM 澶у皬:1 KB 鐗囦笂 ADC:Yes 宸ヤ綔闆绘簮闆诲:1.8 V to 3.6 V 宸ヤ綔婧害鑼冨湇:- 40 C to + 105 C 灏佽 / 绠遍珨:QFN-20 瀹夎棰�(f膿ng)鏍�:SMD/SMT |

| PIC16C621T-20E/SO | 鍔熻兘鎻忚堪:8浣嶅井鎺у埗鍣� -MCU 1.75KB 80 RAM 13 I/O RoHS:鍚� 鍒堕€犲晢:Silicon Labs 鏍稿績:8051 铏曠悊鍣ㄧ郴鍒�:C8051F39x 鏁�(sh霉)鎿�(j霉)绺界窔瀵害:8 bit 鏈€澶ф檪(sh铆)閻橀牷鐜�:50 MHz 绋嬪簭瀛樺劜(ch菙)鍣ㄥぇ灏�:16 KB 鏁�(sh霉)鎿�(j霉) RAM 澶у皬:1 KB 鐗囦笂 ADC:Yes 宸ヤ綔闆绘簮闆诲:1.8 V to 3.6 V 宸ヤ綔婧害鑼冨湇:- 40 C to + 105 C 灏佽 / 绠遍珨:QFN-20 瀹夎棰�(f膿ng)鏍�:SMD/SMT |

| PIC16C621T-20E/SS | 鍔熻兘鎻忚堪:8浣嶅井鎺у埗鍣� -MCU 1.75KB 80 RAM 13 I/O RoHS:鍚� 鍒堕€犲晢:Silicon Labs 鏍稿績:8051 铏曠悊鍣ㄧ郴鍒�:C8051F39x 鏁�(sh霉)鎿�(j霉)绺界窔瀵害:8 bit 鏈€澶ф檪(sh铆)閻橀牷鐜�:50 MHz 绋嬪簭瀛樺劜(ch菙)鍣ㄥぇ灏�:16 KB 鏁�(sh霉)鎿�(j霉) RAM 澶у皬:1 KB 鐗囦笂 ADC:Yes 宸ヤ綔闆绘簮闆诲:1.8 V to 3.6 V 宸ヤ綔婧害鑼冨湇:- 40 C to + 105 C 灏佽 / 绠遍珨:QFN-20 瀹夎棰�(f膿ng)鏍�:SMD/SMT |

| PIC16C621T-20I/SO | 鍔熻兘鎻忚堪:8浣嶅井鎺у埗鍣� -MCU 1.75KB 80 RAM 13 I/O RoHS:鍚� 鍒堕€犲晢:Silicon Labs 鏍稿績:8051 铏曠悊鍣ㄧ郴鍒�:C8051F39x 鏁�(sh霉)鎿�(j霉)绺界窔瀵害:8 bit 鏈€澶ф檪(sh铆)閻橀牷鐜�:50 MHz 绋嬪簭瀛樺劜(ch菙)鍣ㄥぇ灏�:16 KB 鏁�(sh霉)鎿�(j霉) RAM 澶у皬:1 KB 鐗囦笂 ADC:Yes 宸ヤ綔闆绘簮闆诲:1.8 V to 3.6 V 宸ヤ綔婧害鑼冨湇:- 40 C to + 105 C 灏佽 / 绠遍珨:QFN-20 瀹夎棰�(f膿ng)鏍�:SMD/SMT |

鐧�(f膩)甯冪穵鎬ラ噰璩�(g貌u)锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�