- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369995 > PF48F3P0VB00 (Intel Corp.) Intel StrataFlash Embedded Memory PDF資料下載

參數(shù)資料

| 型號(hào): | PF48F3P0VB00 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Embedded Memory |

| 中文描述: | 英特爾StrataFlash嵌入式存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 42/102頁(yè) |

| 文件大小: | 1609K |

| 代理商: | PF48F3P0VB00 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

1-Gbit P30 Family

April 2005

42

Intel StrataFlash

Embedded Memory (P30)

Order Number: 306666, Revision: 001

Datasheet

W14

t

WHGL

WE# high to OE# low

0

-

ns

1,2,9

W16

t

WHQV

WE# high to read valid

t

AVQV

+ 35

-

ns

1,2,3,6,1

0

Write to Asynchronous Read Specifications

W18

t

WHAV

WE# high to Address valid

0

-

ns

1,2,3,6,8

Write to Synchronous Read Specifications

W19

t

WHCH/L

WE# high to Clock valid

19

-

ns

1,2,3,6,1

0

W20

t

WHVH

WE# high to ADV# high

19

-

ns

Write Specifications with Clock Active

W21

t

VHWL

ADV# high to WE# low

-

20

ns

1,2,3,11

W22

t

CHWL

Clock high to WE# low

-

20

ns

Notes:

1.

2.

3.

4.

Write timing characteristics during erase suspend are the same as write-only operations.

A write operation can be terminated with either CE# or WE#.

Sampled, not 100% tested.

Write pulse width low (t

WLWH

or t

ELEH

) is defined from CE# or WE# low (whichever occurs last) to

CE# or WE# high (whichever occurs first). Hence, t

WLWH

= t

ELEH

= t

WLEH

= t

ELWH

.

Write pulse width high (t

WHWL

or t

EHEL

) is defined from CE# or WE# high (whichever occurs first) to

CE# or WE# low (whichever occurs last). Hence, t

WHWL

= t

EHEL

= t

WHEL

= t

EHWL

).

t

WHVH

or t

must be met when transitioning from a write cycle to a synchronous burst read.

V

PP

and WP#

should be at a valid level until erase or program success is determined.

This specification is only applicable when transitioning from a write cycle to an asynchronous read.

See spec W19 and W20 for synchronous read.

When doing a Read Status operation following any command that alters the Status Register, W14 is

20 ns.

Add 10 ns if the write operations results in a RCR or block lock status change, for the subsequent

read operation to reflect this change.

These specs are required only when the device is in a synchronous mode and clock is active during

address setup phase.

5.

6.

7.

8.

9.

10.

11.

Table 18.

AC Write Specifications (Sheet 2 of 2)

Num

Symbol

Parameter

Min

Max

Units

Notes

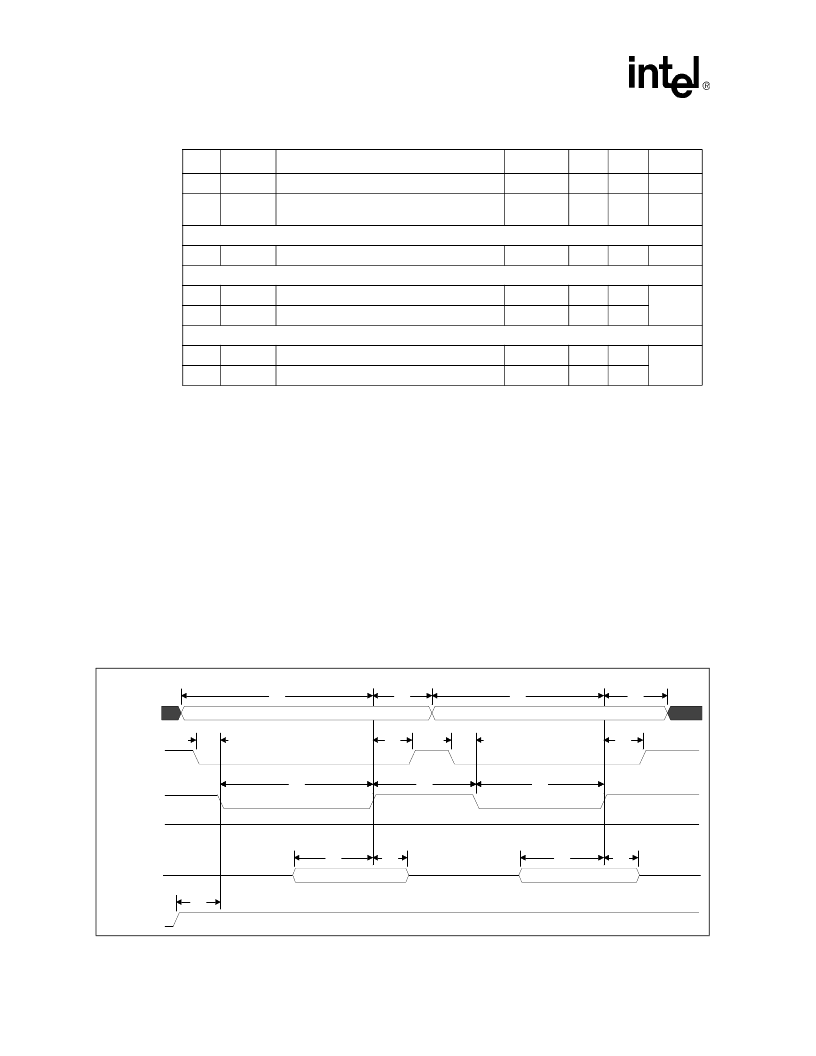

Figure 22.

Write-to-Write Timing

W1

W7

W4

W7

W4

W3

W9

W3

W6

W2

W6

W2

W8

W8

W5

W5

Address [A]

CE# [E}

WE# [W]

OE# [G]

Data [D/Q]

RST# [P]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PF48F4400P0VTQ0 | OSC 5V SMT 7X5 CMOS |

| PF48F4444PPVTQ0 | Intel StrataFlash Embedded Memory |

| PF48F0P0VTQ0 | Intel StrataFlash Embedded Memory |

| PF48F2P0VTQ0 | Intel StrataFlash Embedded Memory |

| PF48F3P0VTQ0 | Intel StrataFlash Embedded Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PF48F3P0VBQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F3P0VT00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F3P0VTQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F3P0ZB00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F3P0ZBQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。