- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369995 > PF48F0P0VTQ0 (Intel Corp.) Intel StrataFlash Embedded Memory PDF資料下載

參數(shù)資料

| 型號: | PF48F0P0VTQ0 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Embedded Memory |

| 中文描述: | 英特爾StrataFlash嵌入式存儲器 |

| 文件頁數(shù): | 59/102頁 |

| 文件大小: | 1609K |

| 代理商: | PF48F0P0VTQ0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當(dāng)前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

1-Gbit P30 Family

Datasheet

Intel StrataFlash

Embedded Memory (P30)

Order Number: 306666, Revision: 001

59

10.3.5

WAIT Delay

The WAIT Delay (WD) bit controls the WAIT assertion-delay behavior during synchronous burst

reads. WAIT can be asserted either during or one data cycle before valid data is output on

DQ[15:0]. When WD is set, WAIT is deasserted one data cycle

before

valid data (default). When

WD is cleared, WAIT is deasserted

during

valid data.

10.3.6

Burst Sequence

The Burst Sequence (BS) bit selects linear-burst sequence (default). Only linear-burst sequence is

supported.

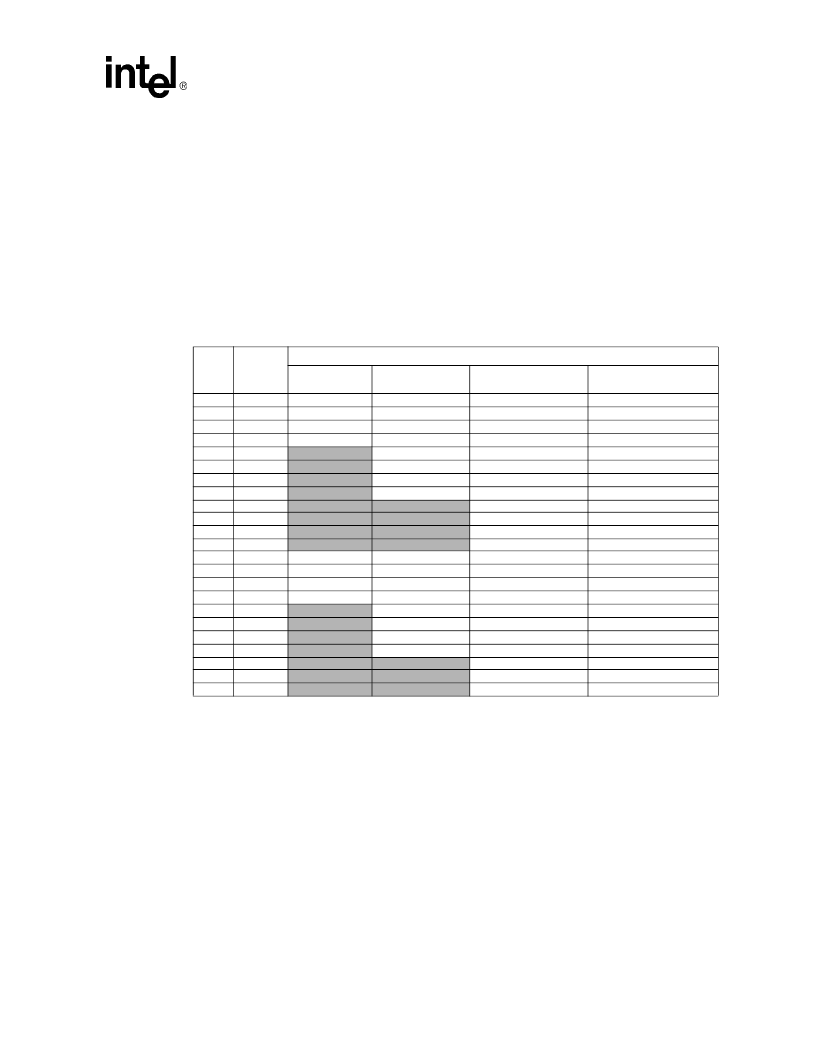

Table 25

shows the synchronous burst sequence for all burst lengths, as well as the

effect of the Burst Wrap (BW) setting.

Burst Sequence Word Ordering

10.3.7

Clock Edge

The Clock Edge (CE) bit selects either a rising (default) or falling clock edge for CLK. This clock

edge is used at the start of a burst cycle, to output synchronous data, and to assert/deassert WAIT.

10.3.8

Burst Wrap

The Burst Wrap (BW) bit determines whether 4-word, 8-word, or 16-word burst length accesses

wrap within the selected word-length boundaries or cross word-length boundaries. When BW is

set, burst wrapping does not occur (default). When BW is cleared, burst wrapping occurs.

When performing synchronous burst reads with BW set (no wrap), an output delay may occur

when the burst sequence crosses its first device-row (16-word) boundary. If the burst sequence’s

start address is 4-word aligned, then no delay occurs. If the start address is at the end of a 4-word

Table 25.

Start

Addr.

(DEC)

Burst Wrap

(RCR[3])

Burst Addressing Sequence (DEC)

4-Word Burst

(BL[2:0] = 0b001)

8-Word Burst

(BL[2:0] = 0b010)

16-Word Burst

(BL[2:0] = 0b011)

Continuous Burst

(BL[2:0] = 0b111)

0

1

2

3

4

5

6

7

…

14

15

…

0

1

2

3

4

5

6

7

…

14

15

0

0

0

0

0

0

0

0

…

0

0

…

1

1

1

1

1

1

1

1

…

1

1

0-1-2-3

1-2-3-0

2-3-0-1

3-0-1-2

0-1-2-3-4-5-6-7

1-2-3-4-5-6-7-0

2-3-4-5-6-7-0-1

3-4-5-6-7-0-1-2

4-5-6-7-0-1-2-3

5-6-7-0-1-2-3-4

6-7-0-1-2-3-4-5

7-0-1-2-3-4-5-6

0-1-2-3-4…14-15

1-2-3-4-5…15-0

2-3-4-5-6…15-0-1

3-4-5-6-7…15-0-1-2

4-5-6-7-8…15-0-1-2-3

5-6-7-8-9…15-0-1-2-3-4

6-7-8-9-10…15-0-1-2-3-4-5 6-7-8-9-10-11-12-…

7-8-9-10…15-0-1-2-3-4-5-6 7-8-9-10-11-12-13…

…

14-15-0-1-2…12-13

15-0-1-2-3…13-14

…

0-1-2-3-4…14-15

1-2-3-4-5…15-16

2-3-4-5-6…16-17

3-4-5-6-7…17-18

4-5-6-7-8…18-19

5-6-7-8-9…19-20

6-7-8-9-10…20-21

7-8-9-10-11…21-22

…

14-15-16-17-18…28-29

15-16-17-18-19…29-30

0-1-2-3-4-5-6-…

1-2-3-4-5-6-7-…

2-3-4-5-6-7-8-…

3-4-5-6-7-8-9-…

4-5-6-7-8-9-10…

5-6-7-8-9-10-11…

…

…

…

14-15-16-17-18-19-20-…

15-16-17-18-19-20-21-…

…

…

…

0-1-2-3

1-2-3-4

2-3-4-5

3-4-5-6

0-1-2-3-4-5-6-7

1-2-3-4-5-6-7-8

2-3-4-5-6-7-8-9

3-4-5-6-7-8-9-10

4-5-6-7-8-9-10-11

5-6-7-8-9-10-11-12

6-7-8-9-10-11-12-13

7-8-9-10-11-12-13-14

…

0-1-2-3-4-5-6-…

1-2-3-4-5-6-7-…

2-3-4-5-6-7-8-…

3-4-5-6-7-8-9-…

4-5-6-7-8-9-10…

5-6-7-8-9-10-11…

6-7-8-9-10-11-12-…

7-8-9-10-11-12-13…

…

…

14-15-16-17-18-19-20-…

15-16-17-18-19-20-21-…

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PF48F2P0VTQ0 | Intel StrataFlash Embedded Memory |

| PF48F3P0VTQ0 | Intel StrataFlash Embedded Memory |

| PF48F4P0VTQ0 | Intel StrataFlash Embedded Memory |

| PF500A-360 | KPT SERIES |

| PF1000A | PFHC module 500W, 1000W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PF48F0P0ZB00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F0P0ZBQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F0P0ZT00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F0P0ZTQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F2000P0ZBQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。