- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367907 > PEEL18CV8P-25 (Electronic Theatre Controls, Inc.) CMOS Programmable Electrically Erasable Logic Device PDF資料下載

參數(shù)資料

| 型號(hào): | PEEL18CV8P-25 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | CMOS Programmable Electrically Erasable Logic Device |

| 中文描述: | 的CMOS電可擦除可編程邏輯器件 |

| 文件頁(yè)數(shù): | 7/10頁(yè) |

| 文件大小: | 411K |

| 代理商: | PEEL18CV8P-25 |

7

04-02-004H

International

CMOS

Technology

PEEL

TM

18CV8

8. Test conditions assume: signal transition times of 3ns or less from the

10% and 90% points, timing reference levels of 1.5V (Unless otherwise

specified).

9. Test one output at a time for a duration of less than 1 second.

10. I

CC

for a typical application: This parameter is tested with the device

programmed as an 8-bit Counter.

11. Parameters are not 100% tested. Specifications are based on initial

characterization and are tested after any design process modification that

might affect operational frequency.

12. Available only for 18CV8 -15/I-15/-25/I-25 grades

13. 24mA available for 18CV8-5/-7. All other speeds are 16mA.

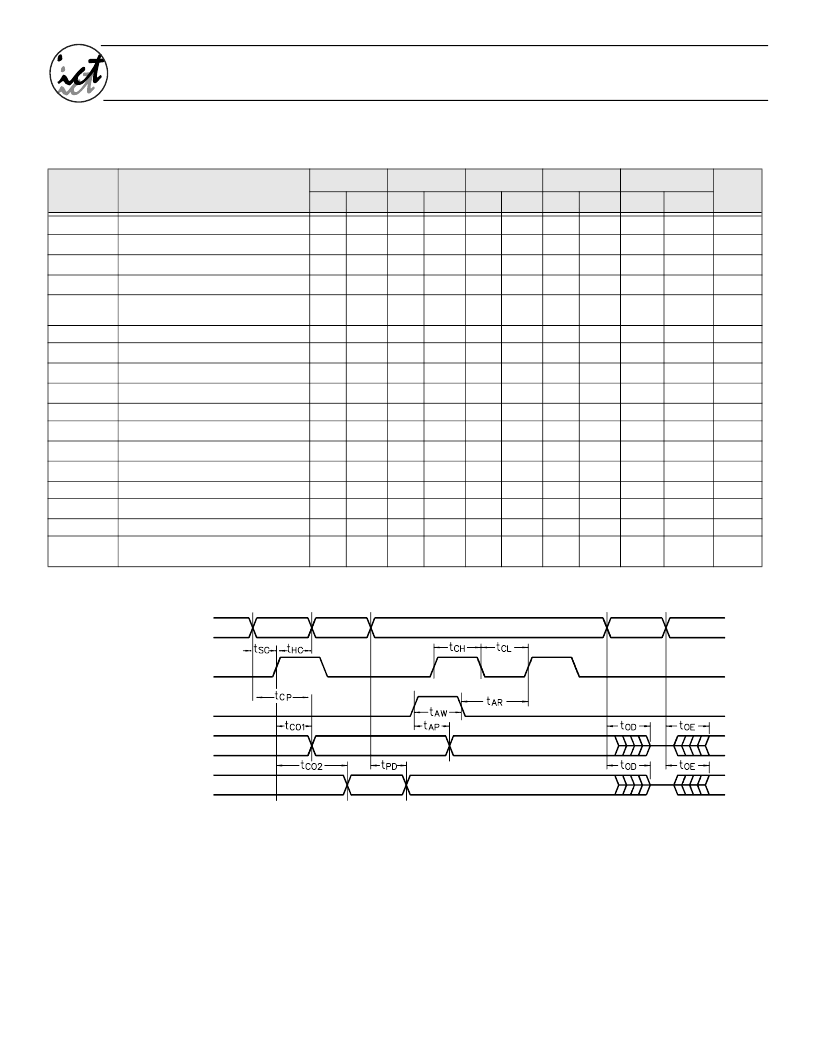

A.C. Electrical Characteristics

Over the operating range

8

Switching Waveforms

Notes:

1. Minimum DC input is -0.5V, however, inputs may undershoot to -2.0V

for periods less than 20 ns.

2. V

I

and V

O

are not specified for program/verify operation.

3. Test Points for Clock and VCC in t

R

and t

F

are referenced at the 10%

and 90% levels.

4. I/O pins are 0V and V

CC

.

5. “Input” refers to an input pin signal.

6. t

OE

is measured from input transition to V

REF

±0.1V, T

OD

is measured

from input transition to V

OH

-0.1V or V

OL

+0.1V; V

REF

=V

L.

7. Capacitances are tested on a sample basis.

Symbol

Parameter

-5

-7

-10/I-10

-15/I-15

-25/I-25

Units

Min Max Min Max Min Max Min Max Min

5

7.5

Max

25

t

PD

t

OE

t

OD

t

CO1

t

CO2

Input

5

to non-registered output

10

15

ns

Input

5

to output enable

6

5

7.5

10

15

25

ns

Input

5

to output disable

6

Clock to Output

5

7.5

10

15

25

ns

4

7

7

12

15

ns

Clock to comb. output delay

via internal registered feedback

Clock to Feedback

7.5

10

12

25

35

ns

t

CF

t

SC

2.5

3.5

4

8

15

ns

ns

Input

5

or feedback setup to clock

3.5

5

5

12

20

t

HC

Input

5

hold after clock

0

0

0

0

0

ns

t

CL

, t

CH

Clock low time, clock high time

8

Min clock period Ext (t

SC

+ t

CO1

)

3

3.5

5

10

15

ns

t

CP

f

MAX1

7

12

12

111

24

50

35

28.5

ns

MHz

Internal feedback (1/t

SC

+t

CF

)

11

166.7

117.6

f

MAX2

External Feedback (1/t

CP

)

11

133

83.3

83.3

41.6

28.5

MHz

f

MAX3

No Feedback (1/t

CL

+t

CH

)

11

Asynchronous Reset Pulse Width

166.7

142.8

100

50

33.3

MHz

t

AW

t

AP

5

7.5

10

15

25

ns

ns

Input

5

to Asynchronous Reset

Asynchronous Reset recovery time

Power-on reset time for registers

in clear state

5

7.5

10

15

25

t

AR

5

7.5

10

15

25

ns

t

RESET

5

5

5

5

5

μs

Inputs, I/O,

Registered Feedback,

Synchronous Preset

Clock

Asynchronous

Reset

Registered

Outputs

Combinatorial

Outputs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PEEL18CV8P-7 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL18CV8J-10 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL18CV8J-15 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL18CV8TI-10 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL18CV8TI-15 | CMOS Programmable Electrically Erasable Logic Device |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PEEL18CV8P-25L | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 10 INP 8 I/O 25ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PEEL18CV8P-30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable PLD |

| PEEL18CV8P-35 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable PLD |

| PEEL18CV8P-5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Programmable Electrically Erasable Logic Device |

| PEEL18CV8P50 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。