- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394P11BD (NXP SEMICONDUCTORS) 3-port physical layer interface PDF資料下載

參數(shù)資料

| 型號: | PDI1394P11BD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | 3-port physical layer interface |

| 中文描述: | TRIPLE LINE TRANSCEIVER, PQFP64 |

| 文件頁數(shù): | 8/42頁 |

| 文件大?。?/td> | 233K |

| 代理商: | PDI1394P11BD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

8

6.0

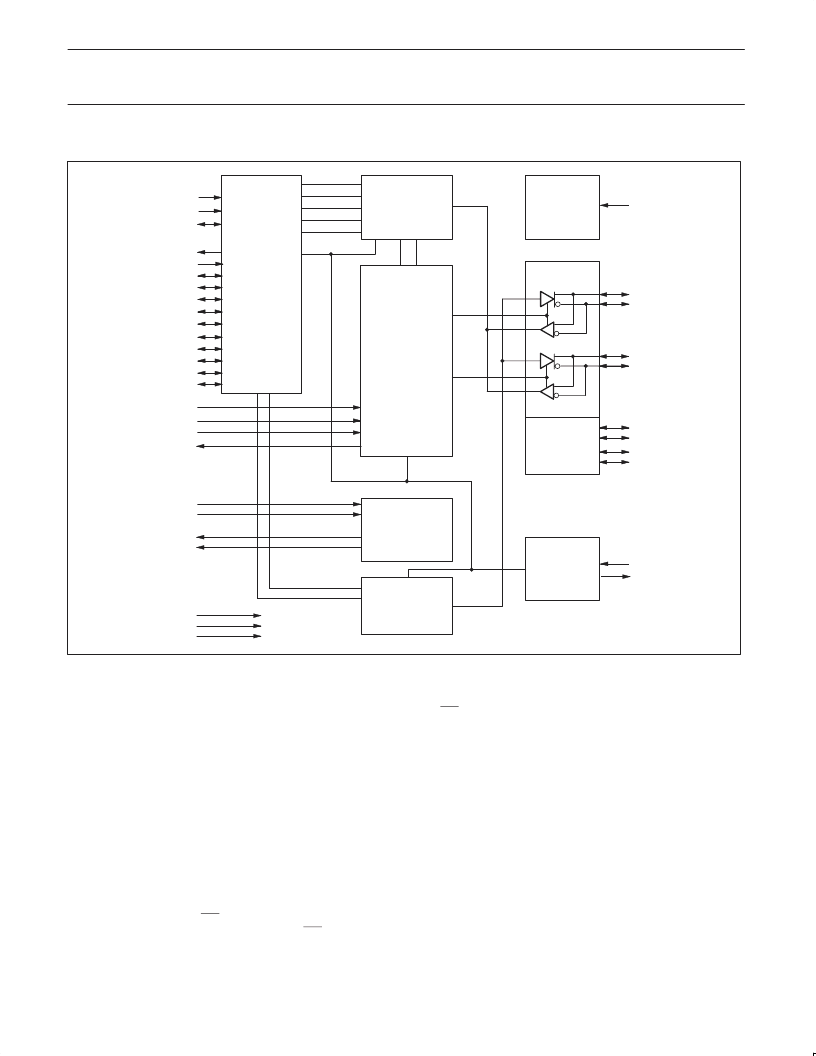

BLOCK DIAGRAM

CABLE PORT 0

CABLE PORT 1

RECEIVED DATA

DECODER/

RETIMER

LINK

INTERFACE

I/O

ARBITRATION

AND CONTROL

STATE MACHINE

LOGIC

CRYSTAL

OSCILLATOR,

PLL SYSTEM,

AND CLOCK

GENERATOR

TRANSMIT

DATA

ENCODER

CNA

PC0

PC1

PC2

D0

D1

D2

D3

D4

D5

D6

D7

CTL0

CTL1

LREQ

SYSCLK

C/LKON

/ISO

LPS

/RESET

PD

TPA0+

TPA0–

TPB0+

TPB0–

TPA1+

TPA1–

TPB1+

TPB1–

XI

XO

SV01785

BIAS VOLTAGE

AND

CURRENT

GENERATOR

R0

R1

TPBIAS0

TPBIAS1

CABLE POWER

DETECTOR

CPS

TWOPORT

7.0

The PDI1394P23 requires only an external 24.576 MHz crystal as a

reference. An external clock can be connected to XI instead of a

crystal. An internal oscillator drives an internal phase-locked loop

(PLL), which generates the required 393.216 MHz reference signal.

This reference signal is internally divided to provide the clock signals

used to control transmission of the outbound encoded Strobe and

Data information. A 49.152 MHz clock signal, supplied to the

associated LLC for synchronization of the two chips, is used for

resynchronization of the received data. The Power Down (PD)

function, when enabled by asserting the PD terminal high, stops

operation of the PLL and disables all circuits except the cable bias

detectors at the TPB terminals. The port transmitter circuitry and the

receiver circuitry are also disabled when the port is disabled,

suspended, or disconnected.

FUNCTIONAL SPECIFICATION

The PDI1394P23 supports an optional isolation barrier between

itself and its LLC. When the ISO input terminal is tied high, the

LLC interface outputs behave normally. When the ISO terminal is

tied low, internal differentiating logic is enabled, and the outputs are

driven such that they can be coupled through a capacitive or

transformer galvanic isolation barrier as described in IEEE 1394a

section 5.9.4 To operate with single capacitor (bus holder) isolation,

the ISO on the PHY terminal must be tied high. For more details on

using single capacitor isolation, please refer to the Philips Isolation

Application Note AN2452.

Data bits to be transmitted through the cable ports are received from

the LLC on two, four or eight parallel paths (depending on the

requested transmission speed). They are latched internally in the

PDI1394P23 in synchronization with the 49.152 MHz system clock.

These bits are combined serially, encoded, and transmitted at

98.304/196.608/393.216 Mbps (referred to as S100, S200, and

S400 speed, respectively) as the outbound data-strobe information

stream. During transmission, the encoded data information is

transmitted differentially on the TPB cable pair(s), and the encoded

strobe information is transmitted differentially on the TPA cable

pair(s).

During packet reception the TPA and TPB transmitters of the

receiving cable port are disabled, and the receivers for that port are

enabled. The encoded data information is received on the TPA cable

pair, and the encoded strobe information is received on the TPB

cable pair. The received data-strobe information is decoded to

recover the receive clock signal and the serial data bits. The serial

相關PDF資料 |

PDF描述 |

|---|---|

| PDI1394P25 | 1-port 400 Mbps physical layer interface |

| PDI1394P25BD | 1-port 400 Mbps physical layer interface |

| PDI1394P25EC | 1-port 400 Mbps physical layer interface |

| PDI1394P23BD | 2-port/1-port 400 Mbps physical layer interface |

| PDI1394L41BE | 8358 PBGA ENCRP NO-PB |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394P11BD-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Transceiver |

| PDI1394P21 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P21BE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P22 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P22BD | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

發(fā)布緊急采購,3分鐘左右您將得到回復。