- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369957 > PD64012 (Electronic Theatre Controls, Inc.) 12-channel PoE Manager PDF資料下載

參數(shù)資料

| 型號: | PD64012 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 12-channel PoE Manager |

| 中文描述: | 12通道供電管理 |

| 文件頁數(shù): | 6/16頁 |

| 文件大?。?/td> | 496K |

| 代理商: | PD64012 |

PD64012

12-CHANNEL PoE MANAGER

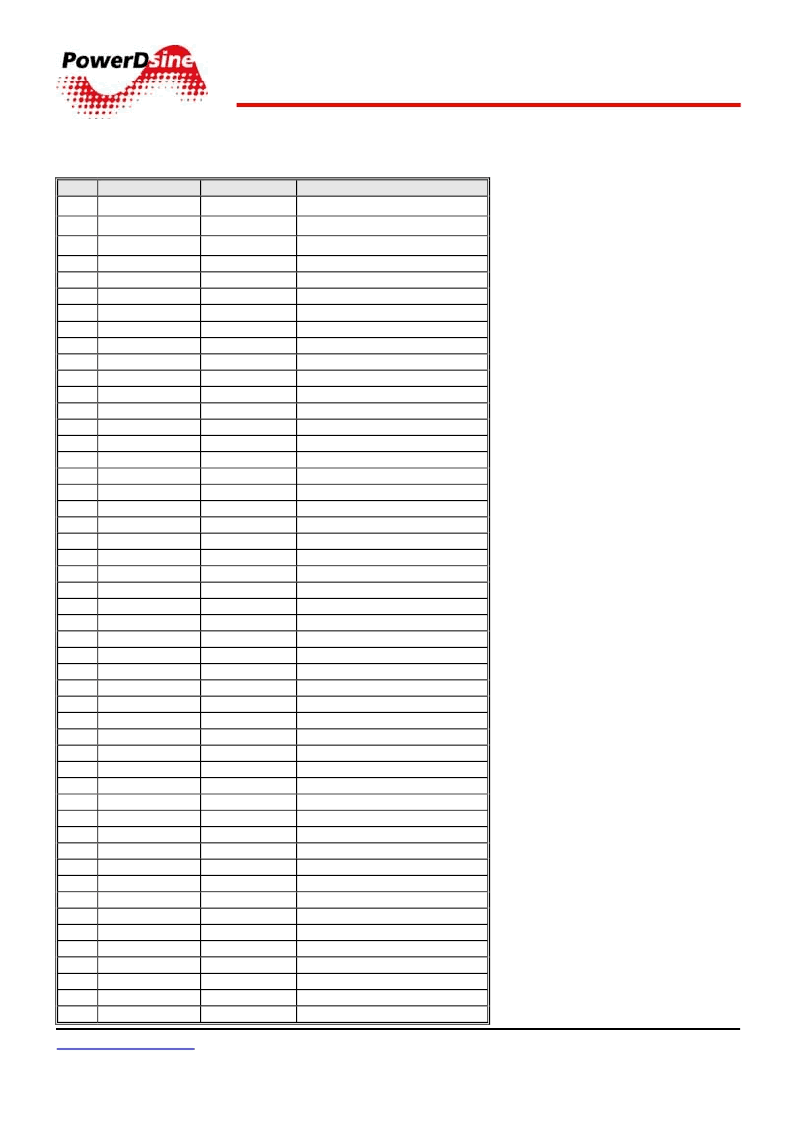

Pins Descriptions ______________________________________________

PIN

PIN NAME

PIN TYPE

PIN DESCRIPTION

1.

V

PORT_POS0

Analog I/O

Port 0 positive voltage feeding

2.

V

PORT_POS1

Analog I/O

Port 1 positive voltage feeding

3.

V

PORT_POS2

Analog I/O

Port 2 positive voltage feeding

4.

V

PORT_POS3

Analog I/O

Port 3 positive voltage feeding

5.

V

PORT_POS4

Analog I/O

Port 4 positive voltage feeding

6.

V

PORT_POS5

Analog I/O

Port 5 positive voltage feeding

7.

V

PORT_POS6

Analog I/O

Port 6 positive voltage feeding

8.

V

PORT_POS7

Analog I/O

Port 7 positive voltage feeding

9.

V

PORT_POS8

Analog I/O

Port 8 positive voltage feeding

10.

V

PORT_POS9

Analog I/O

Port 9 positive voltage feeding

11.

V

PORT_POS10

Analog I/O

Port 10 positive voltage feeding

12.

V

PORT_POS11

Analog I/O

Port 11 positive voltage feeding

13.

V

main

Supply

Main Voltage supply

14.

CP_IN

Analog I/O

Charge Pump input, 48V+5V

15.

CP_OUT

Analog I/O

Charge Pump Pulse Output

16.

REF_PORT_NEG Analog I/O

Port negative reference

17.

TEST_MODE

Analog I/O

Test Mode Pin (connect to ground)

18.

V

PORT_NEG11

Analog I/O

Port 11 negative voltage feeding

19.

AGND

Supply

Analog ground

20.

PORT_SENSE11

Analog I/O

Channel current monitoring

21.

V

PORT_NEG10

Analog I/O

Port 10 negative voltage feeding

22.

PORT_SENSE10

Analog I/O

Channel current monitoring

23.

V

PORT_NEG9

Analog I/O

Port 9 negative voltage feeding

24.

PORT_SENSE9

Analog I/O

Channel current monitoring

25.

PORT_SENSE8

Analog I/O

Channel current monitoring

26.

V

PORT_NEG8

Analog I/O

Port 8 negative voltage feeding

27.

PORT_SENSE7

Analog I/O

Channel current monitoring

28.

V

PORT_NEG7

Analog I/O

Port 7 negative voltage feeding

29.

PORT_SENSE6

Analog I/O

Channel current monitoring

30.

DISABLE_PORTS_N

Digital input

Disable all ports power (active low)

31.

V

PORT_NEG6

Analog I/O

Port 6 negative voltage feeding

32.

CS1_N

Digital I/O

SPI bus, Chip Select 1

33.

DGND

Supply

Digital ground

34.

CS0_N

Digital I/O

SPI bus, Chip Select 0

35.

MISO

Digital I/O

SPI bus, Master in/slave out

36.

MOSI

Digital I/O

SPI bus, Master out/slave in

37.

SCK

Digital input

SPI bus, Serial clock I/O

38.

SCL

Digital input

I2C bus, Serial Clock Input

39.

SDA

Digital I/O

I2C bus, open drain

40.

RESET_N

Digital I/O

Active Low Reset I/O

41.

IREF

Analog I/O

Current reference

42.

ASICINI

Analog input

Analog input for ASIC initialization

43.

VCC

2p5

Supply

Internal 2.5 V supply (do not use!)

44.

I2CINI

Analog input

Analog input for I2C initialization

45.

QGND

Supply

Quiet analog ground

46.

ADC

2p5

Supply

ADC reference (do not use!)

47.

EXT_REG

Analog out

External regulation

48.

V

PERI

Analog out

Regulated 3.3 V power source

49.

Reserved

Digital input

(Connect to ground)

50.

V

PORT_NEG5

Analog I/O

Port 5 negative voltage feeding

www.powerdsine.com

06-0003-058 (Rev. 2.8) / 5 August 2004

PowerDsine 2003

Information in this document subject

to change without prior notice.

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PD65-25MC | Analog IC |

| PD65-10HC | Analog IC |

| PD65-10LC | Analog IC |

| PD65-10MC | Analog IC |

| PD65-12HC | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD64012G | 制造商:Microsemi Corporation 功能描述:POE PSE MANAGER - Bulk |

| PD64012GH | 制造商:Microsemi Corporation 功能描述:POE PSE MANAGER - Bulk |

| PD640G63UI | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Read/Write Flash Memory with Enhanced VersatileIOTM Control |

| PD640G63VI | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Read/Write Flash Memory with Enhanced VersatileIOTM Control |

| PD640G73UI | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Read/Write Flash Memory with Enhanced VersatileIOTM Control |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。