- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369950 > PCK2002 (NXP Semiconductors N.V.) 0-300 MHz I2C 1:18 clock buffer PDF資料下載

參數(shù)資料

| 型號: | PCK2002 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 0-300 MHz I2C 1:18 clock buffer |

| 中文描述: | 0-300 MHz的時(shí)鐘緩沖器的I2C 1:18 |

| 文件頁數(shù): | 7/12頁 |

| 文件大小: | 95K |

| 代理商: | PCK2002 |

Philips Semiconductors

Product data

PCK2002

0–300 MHz I

2

C 1:18 clock buffer

2001 Jul 19

7

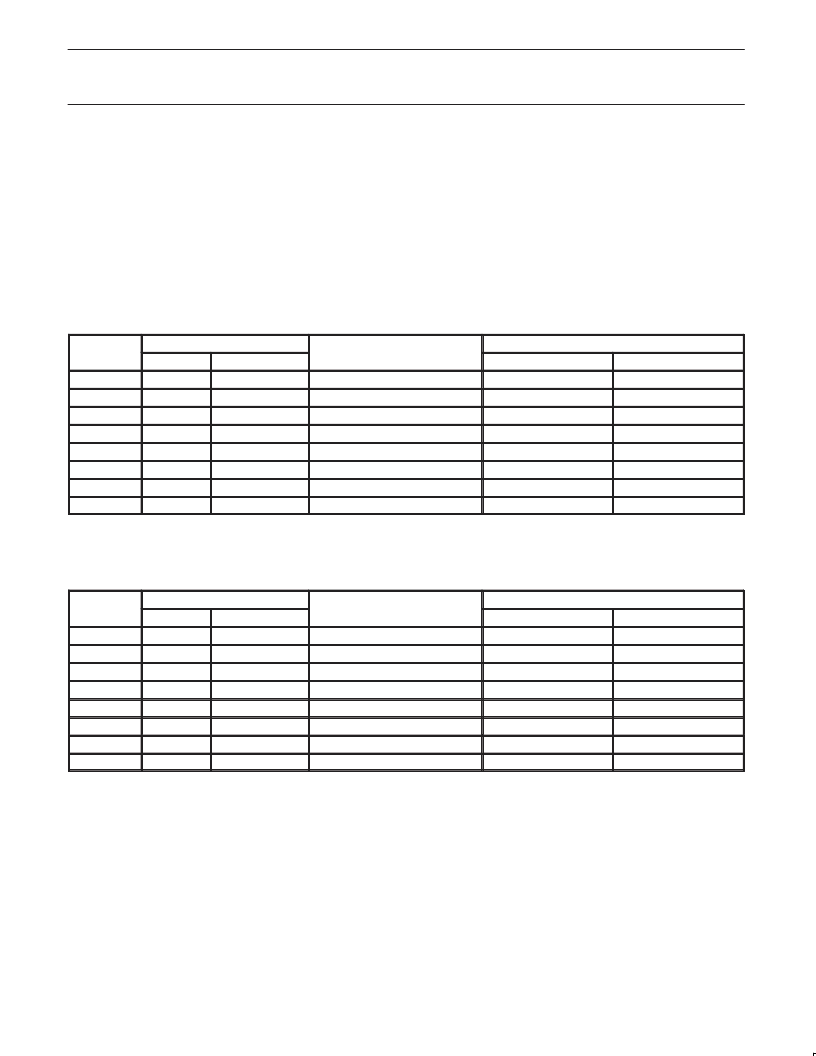

SERIAL CONFIGURATION MAP

The serial bits will be read by the clock buffer in the following order:

Byte 0 – Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte 1 – Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte 2 – Bits 7, 6, 5, 4, 3, 2, 1, 0

All unused register bits (Reserved and N/A) should be desined as “Don’t Care”. It is expected that the controller will force all of these bits to a

“0” level.

All register bits labeled “Initialize to 0” must be written to zero during intialization. Failure to do so may result in a higher than normal operating

current. The controller will read back the last written value.

Byte 0:

1 = enable; 0 = disable

SDRAM Output active/inactive register

BIT(S)

AFFECTED PIN

PIN NO.

CONTROL FUNCTION

BIT CONTROL

PIN NAME

0

1

7

18

BUF_OUT7

Clock Output Disable

Low

Active

6

17

BUF_OUT6

Clock Output Disable

Low

Active

5

14

BUF_OUT5

Clock Output Disable

Low

Active

4

13

BUF_OUT4

Clock Output Disable

Low

Active

3

9

BUF_OUT3

Clock Output Disable

Low

Active

2

8

BUF_OUT2

Clock Output Disable

Low

Active

1

5

BUF_OUT1

Clock Output Disable

Low

Active

0

4

BUF_OUT0

Clock Output Disable

Low

Active

NOTE:

1. At power up all SDRAM outputs are enabled and active. Program all reserved bits to “0”.

Byte 1:

1 = enable; 0 = disable

SDRAM Output active/inactive register

BIT(S)

AFFECTED PIN

CONTROL FUNCTION

BIT CONTROL

PIN NO.

PIN NAME

0

1

7

45

BUF_OUT15

Clock Output Disable

Low

Active

6

44

BUF_OUT14

Clock Output Disable

Low

Active

5

41

BUF_OUT13

Clock Output Disable

Low

Active

4

40

BUF_OUT12

Clock Output Disable

Low

Active

3

36

BUF_OUT11

Clock Output Disable

Low

Active

2

35

BUF_OUT10

Clock Output Disable

Low

Active

1

32

BUF_OUT9

Clock Output Disable

Low

Active

0

31

BUF_OUT8

Clock Output Disable

Low

Active

NOTE:

1. At power up all SDRAM outputs are enabled and active. Program all reserved bits to “0”.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCK2002DGG | 0-300 MHz I2C 1:18 clock buffer |

| PCK857DGG | 66-150MHz Phase Locked Loop Differential 1:10 SDRAM Clock Driver |

| PCKV857A | 100-250 MHz differential 1:10 clock driver |

| PCKV857ADGG | 100-250 MHz differential 1:10 clock driver |

| PCKV857ADGV | 100-250 MHz differential 1:10 clock driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCK2002DGG | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:0-300 MHz I2C 1:18 clock buffer |

| PCK2002DGG,112 | 功能描述:時(shí)鐘緩沖器 14.318-167MHZ I2C 1:18 CLK BUF RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| PCK2002DL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:0-300 MHz I2C 1:18 clock buffer |

| PCK2002DL,112 | 功能描述:時(shí)鐘緩沖器 14.318-167MHZ I2C 1:18 CLK BUF RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| PCK2002DL,118 | 功能描述:時(shí)鐘緩沖器 14.318-167MHZ I2C 1:18 CLK BUF RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。