- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369950 > PCK12429A (NXP SEMICONDUCTORS) 25-400 MHz differential PECL clock generator PDF資料下載

參數(shù)資料

| 型號: | PCK12429A |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | XO, clock |

| 英文描述: | 25-400 MHz differential PECL clock generator |

| 中文描述: | 400 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁數(shù): | 5/14頁 |

| 文件大小: | 128K |

| 代理商: | PCK12429A |

Philips Semiconductors

Product data

PCK12429

25–400 MHz differential PECL clock generator

2002 Jun 03

5

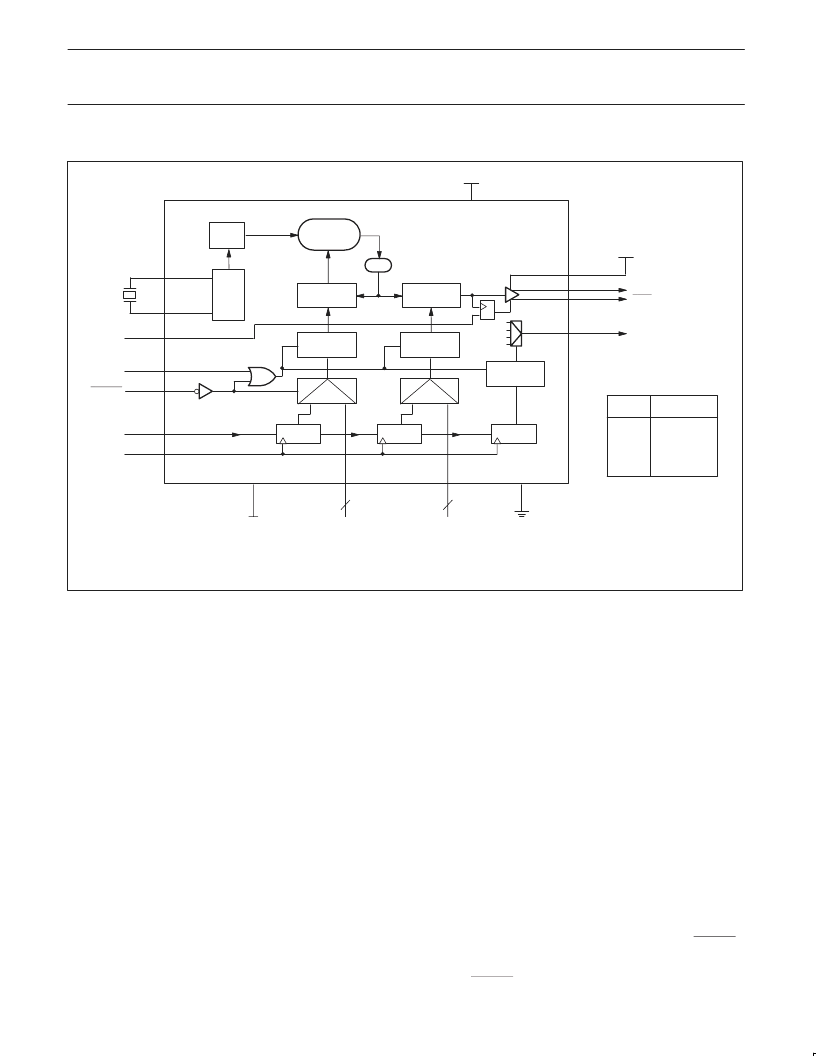

BLOCK DIAGRAM

XTAL1

SW00728

OSC

XTAL2

DIV 16

1 MHz

F

REF

PHASE

DETECTOR

VCO

9-BIT DIV M

COUNTER

LATCH

200–400

MHz

DIV N

(1, 2, 4, 8)

V

CC0

+3.3 V

LATCH

F

OUT

F

OUT

16 MHz

OE

0

1

0

1

LATCH

TEST

S_LOAD

P_LOAD

9-BIT

SR

2-BIT

SR

3-BIT

SR

S_DATA

S_CLOCK

V

CC1

+3.3 V

9

M[8:0]

2

N[1:0]

+3.3 V

PLL_V

CC

N[1:0]

Output Division

0 0

0 1

1 0

1 1

1

2

4

8

PROGRAMMING INTERFACE

Programming the device amounts to properly configuring the internal

dividers to produce the desired frequency at the outputs. The output

frequency can be represented by this formula:

F

OUT

= (F

XTAL

÷

16)

×

M

÷

N

(1)

Where F

XTAL

is the crystal frequency, M is the loop divider modulus,

and N is the output divider modulus. Note that it is possible to select

values of M such that the PLL is unable to achieve loop lock. To

avoid this, always make sure that M is selected to be 200

≤

M

≤

400

for a 16 MHz input reference.

Assuming that a 16 MHz reference frequency is used, the above

equation reduces to:

F

OUT

= M

÷

N

Substituting the four values for N (1, 2, 4, or 8) yields:

F

OUT

= M, F

OUT

= M

÷

2,

F

OUT

= M

÷

4 and F

OUT

= M

÷

8

for 200

≤

M

≤

400

The user can identify the proper M and N values for the desired

frequency from the above equations. The four output frequency

ranges established by N are 200–400 MHz, 100–200 MHz,

50–100 MHz, and 25–50 MHz respectively. From these ranges the

user will establish the value of N required, then the value of M can

be calculated based on the appropriate equation above. For

example, if an output frequency of 131 MHz was desired, the

following steps would be taken to identify the appropriate M and N

values. 131 MHz falls within the frequency range set by an N value

of 2 so N [1:0] = 01. For N = 2 F

OUT

= M

÷

2 and M = 2

×

F

OUT

.

Therefore, M = 131

×

2 = 262, so M[8:0] = 100000110. Following this

same procedure a user can generate any whole frequency desired

between 25 and 400 MHz. Note that for N

≥

2 fractional values of

F

OUT

can be realized. The size of the programmable frequency

steps (and thus the indicator of the fractional output frequencies

achievable) will be equal to F

XTAL

÷

16

÷

N.

For input reference frequencies other than 16 MHz, the set of

appropriate equations can be deduced from equation 1. For

computer applications another useful frequency base would be

16.666 MHz. From this reference, one can generate a family of

output frequencies at multiples of the 33.333 MHz PCI clock. As an

example, to generate a 133.333 MHz clock from a 16.666 MHz

reference, the following M and N values would be used:

F

OUT

= 16.666

÷

16

×

M

÷

N = 1.041625

×

M

÷

N

Let N = 2, M = 256,

F

OUT

= 1.041625

×

256

÷

2 = 133.328 MHz

The value for M falls within the constraints set for PLL stability,

therefore N[1:0] = 01 and M[8:0] = 100000000. If the value for M fell

outside of the valid range a different N value would be selected to try

to move M in the appropriate direction.

The M and N counters can be loaded either through a parallel or

serial interface. The parallel interface is controlled via the P_LOAD

signal such that a LOW to HIGH transition will latch the information

present on the M[8:0] and N[1:0] inputs into the M and N counters.

When the P_LOAD signal is LOW the input latches will be

transparent and any changes on the M[8:0] and N[1:0] inputs will

相關PDF資料 |

PDF描述 |

|---|---|

| PCK12429BD | 25-400 MHz differential PECL clock generator |

| PCK12429D | 25-400 MHz differential PECL clock generator |

| PCK2000MDB | CK97 66/100MHz Mobile System Clock Generator |

| PCK2001MDB | 14.318-150 MHz I2C 1:10 Clock Buffer |

| PCK2002M | 0-300 MHz I2C 1:10 clock buffer |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PCK12429A,112 | 功能描述:鎖相環(huán) - PLL 25-400 MHZ DIFF PECL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| PCK12429A,118 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 25-400 MHZ DIFF PECL RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PCK12429A-T | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 25-400 MHZ DIFF PECL CLOCK GEN RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PCK12429BD | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 25-400MHZ DIFF PECL CLOCK GEN RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PCK12429BD,118 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 25-400MHZ DIFF PECL RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購,3分鐘左右您將得到回復。