- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367816 > PCF211410 (NXP Semiconductors N.V.) LCD controller/drivers(LCD控制器/驅(qū)動(dòng)器) PDF資料下載

參數(shù)資料

| 型號(hào): | PCF211410 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | LCD controller/drivers(LCD控制器/驅(qū)動(dòng)器) |

| 中文描述: | LCD控制器/驅(qū)動(dòng)器(液晶顯示控制器/驅(qū)動(dòng)器) |

| 文件頁(yè)數(shù): | 8/64頁(yè) |

| 文件大?。?/td> | 407K |

| 代理商: | PCF211410 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

1997 Apr 07

8

Philips Semiconductors

Product specification

LCD controller/drivers

PCF2116 family

8.2

LCD supply voltage generator, PCF2116K

In the PCF2116K version, V

0

is connected through an

on-chip resistor (R

0

) to V

LCD

. Resistor R

0

has a nominal

value of 1 M

and draws a typical current of 4

μ

A from the

pin V

0

. A constant voltage (equal to 1.34V

DD

) is always

present across R

0

.

The voltage range of the PCF2116K is between V

SS

and

V

DD

0.5 V (see Fig.4). When V

0

is connected to V

DD

the

generator is switched off and an external voltage must be

supplied to pin V

LCD

. This may be more negative than V

SS

.

When G = logic 1 the generator produces a negative

voltage at pin V

LCD

, controlled by the input voltage at

pin V

0

. The LCD operating voltage is given by the

relationship:

V

OP

= 2.34V

DD

V

0

Where:

V

OP

= V

DD

V

LCD

V

LCD

= V

0

(1.34V

DD

)

When G = logic 0, the generated output voltage V

LCD

is

equal to V

0

(between V

SS

and V

DD

). In this instance:

V

OP

= V

DD

V

0

8.3

Character generator ROM (CGROM)

The standard character sets A, C and G are available for

the PCF2114x and PCF2116x. Standard character set C is

available for the PCF2116K.

8.4

LCD bias voltage generator

The intermediate bias voltages for the LCD display are

also generated on-chip. This removes the need for an

external resistive bias chain and significantly reduces the

system power consumption. The optimum levels depend

on the multiplex rate and are selected automatically when

the number of lines in the display is defined.

The optimum value of V

OP

depends on the multiplex rate,

the LCD threshold voltage (V

th

) and the number of bias

levels and is given by the relationships in Table 1.Using a

5-level bias scheme for 1 : 16 MUX rate allows V

OP

< 5 V

for most LCD liquids. The effect on the display contrast is

negligible.

8.5

Oscillator

The on-chip oscillator provides the clock signal for the

display system. No external components are required.

Pin OSC must be connected to V

DD

.

8.6

External clock

If an external clock is to be used, it must be input at

pin OSC. The resulting display frame frequency is given by

f

frame

=

1

2304

f

osc

. A clock signal must always be present,

otherwise the LCD may be frozen in a DC state.

8.7

Power-on reset

The power-on reset block initializes the chip after

power-on or power failure.

8.8

Registers

The PCF2116 has two 8-bit registers, an Instruction

Register (IR) and a Data Register (DR). The Register

Select signal (RS) determines which register will be

accessed.

The instruction register stores instruction codes such as

‘Display clear’ and ‘Cursor shift’, and address information

for the Display Data RAM (DDRAM) and Character

Generator RAM (CGRAM). The instruction register can be

written to, but not read, by the system controller.

The data register temporarily stores data to be read from

the DDRAM and CGRAM. When reading, data from the

DDRAM or CGRAM corresponding to the address in the

Address Counter is written to the data register prior to

being read by the ‘Read data’ instruction.

8.9

Busy Flag

The Busy Flag indicates the free/busy status of the

PCF2116. Logic 1 indicates that the chip is busy and

further instructions will not be accepted. The Busy Flag is

output to pin DB7 when RS = logic 0 and R/W = logic 1.

Instructions should only be written after checking that the

Busy Flag is logic 0 or waiting for the required number of

clock cycles.

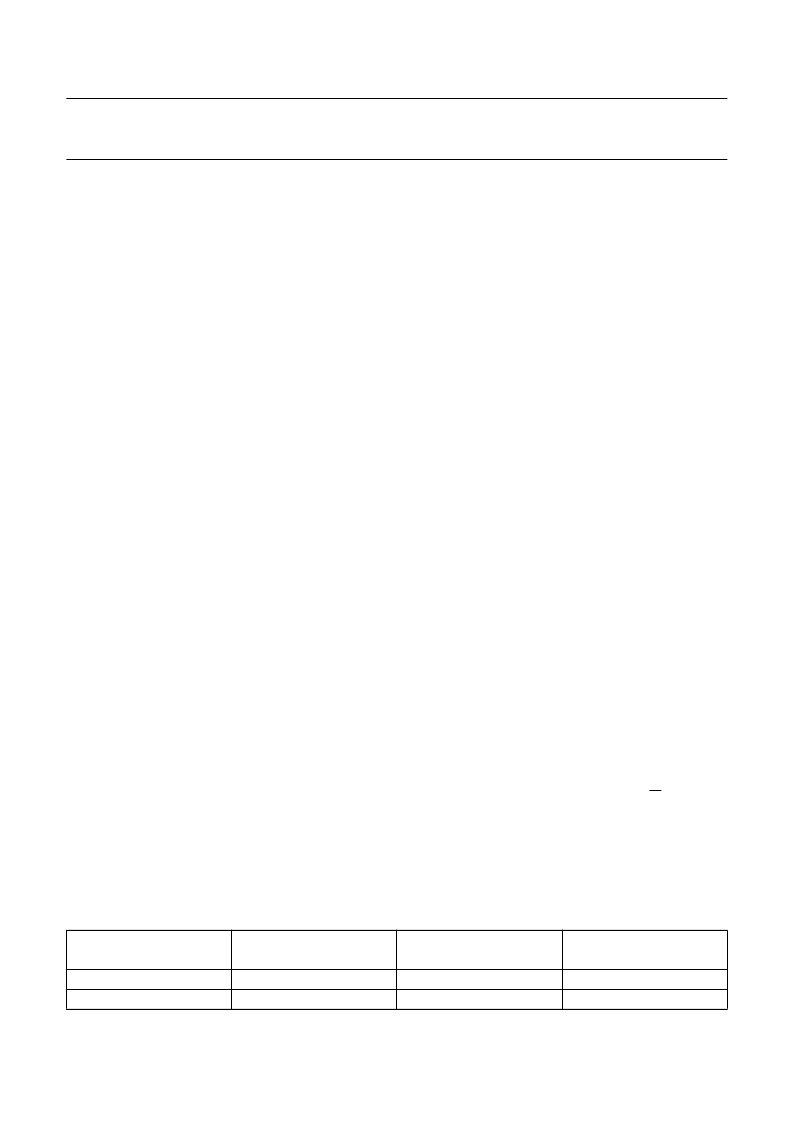

Table 1

Optimum values for V

OP

MUX RATE

NUMBER OF BIAS

LEVELS

V

OP

/V

th

DISCRIMINATION

V

on

/V

off

1.277

1.196

1 : 16

1 : 32

5

6

3.67

5.19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF2116AHZ | JT 66C 66#22D PIN RECP |

| PCF2116CHZ | LCD controller/drivers |

| PCF211412 | LCD controller/drivers(LCD控制器/驅(qū)動(dòng)器) |

| PCF2114xU | LCD controller/drivers(LCD控制器/驅(qū)動(dòng)器) |

| PCF211610 | LCD controller/drivers(LCD控制器/驅(qū)動(dòng)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF2114AH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| PCF2114AU | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| PCF2114AU/10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:LCD controller/drivers |

| PCF2114AU/12 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:LCD controller/drivers |

| PCF2114CH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。