- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369946 > PALC22V10-25WC (CYPRESS SEMICONDUCTOR CORP) Flash-erasable Reprogrammable CMOS PAL Device PDF資料下載

參數(shù)資料

| 型號: | PALC22V10-25WC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | Flash-erasable Reprogrammable CMOS PAL Device |

| 中文描述: | UV PLD, 25 ns, CDIP24 |

| 封裝: | 0.300 INCH, WINDOWED, CERDIP-24 |

| 文件頁數(shù): | 2/13頁 |

| 文件大?。?/td> | 367K |

| 代理商: | PALC22V10-25WC |

PALCE22V10

USE ULTRA37000

TM

FOR

ALL NEW DESIGNS

Document #: 38-03027 Rev. *B

Page 2 of 13

Functional Description

The Cypress PALCE22V10 is a CMOS Flash-erasable

second-generation programmable array logic device. It is

implemented with the familiar sum-of-products (AND-OR)

logic structure and the programmable macrocell.

The PALCE22V10 is executed in a 24-pin 300-mil molded DIP,

a 300-mil cerDIP, a 28-lead square ceramic leadless chip

carrier, a 28-lead square plastic leaded chip carrier, and

provides up to 22 inputs and 10 outputs. The PALCE22V10

can be electrically erased and reprogrammed. The program-

mable macrocell provides the capability of defining the archi-

tecture of each output individually. Each of the ten potential

outputs may be specified as “registered” or “combinatorial.”

Polarity of each output may also be individually selected,

allowing complete flexibility of output configuration. Further

configurability is provided through “array” configurable “output

enable” for each potential output. This feature allows the 10

outputs to be reconfigured as inputs on an individual basis, or

alternately used as a combination I/O controlled by the

programmable array.

PALCE22V10 features a variable product term architecture.

There are 5 pairs of product term sums beginning at 8 product

terms per output and incrementing by 2 to 16 product terms

per output. By providing this variable structure, the

PALCE22V10 is optimized to the configurations found in a

majority of applications without creating devices that burden

the product term structures with unusable product terms and

lower performance.

Additional features of the Cypress PALCE22V10 include a

synchronous preset and an asynchronous reset product term.

These product terms are common to all macrocells, elimi-

nating the need to dedicate standard product terms for initial-

ization functions. The device automatically resets upon

power-up.

The PALCE22V10, featuring programmable macrocells and

variable product terms, provides a device with the flexibility to

implement logic functions in the 500- to 800-gate-array

complexity. Since each of the ten output pins may be individ-

ually configured as inputs on a temporary or permanent basis,

functions requiring up to 21 inputs and only a single output and

down to twelve inputs and ten outputs are possible. The ten

potential outputs are enabled using product terms. Any output

pin may be permanently selected as an output or arbitrarily

enabled as an output and an input through the selective use

of individual product terms associated with each output. Each

of these outputs is achieved through an individual program-

mable macrocell. These macrocells are programmable to

provide a combinatorial or registered inverting or non-inverting

output. In a registered mode of operation, the output of the

register is fed back into the array, providing current status

information to the array. This information is available for estab-

lishing the next result in applications such as control state

machines. In a combinatorial configuration, the combinatorial

output or, if the output is disabled, the signal present on the I/O

pin is made available to the array. The flexibility provided by

both programmable product term control of the outputs and

variable product terms allows a significant gain in functional

density through the use of programmable logic.

Along with this increase in functional density, the Cypress

PALCE22V10 provides lower-power operation through the use

of CMOS technology, and increased testability with Flash

reprogrammability.

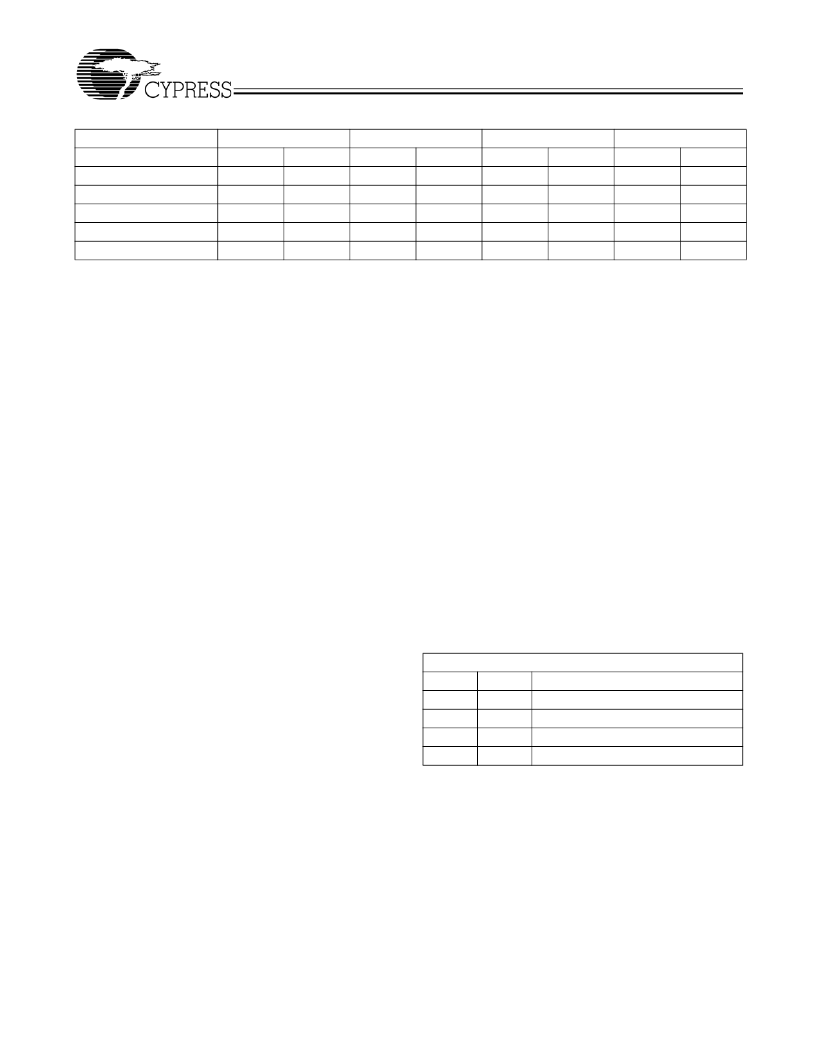

Selection Guide

Generic Part Number

t

PD

ns

t

S

ns

t

CO

ns

I

CC

mA

Com’l

5

7.5

10

15

25

Mil/Ind

Com’l

3

5

6

10

15

Mil/Ind

Com’l

4

5

7

8

15

Mil/Ind

Com’l

130

130

90

90

90

Mil/Ind

PALCE22V10-5

PALCE22V10-7

PALCE22V10-10

PALCE22V10-15

PALCE22V10-25

10

15

25

6

10

15

7

8

150

120

120

15

Configuration Table

Registered/Combinatorial

C

0

0

Registered/Active LOW

1

Registered/Active HIGH

0

Combinatorial/Active LOW

1

Combinatorial/Active HIGH

C

1

0

0

1

1

Configuration

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PALCE22V10-15PI | Flash-erasable Reprogrammable CMOS PAL Device |

| PALCE22V10-25DMB | Flash-erasable Reprogrammable CMOS PAL Device |

| PALCE22V10-25KMB | Flash-erasable Reprogrammable CMOS PAL Device |

| PALCE22V10-25PI | Flash-erasable Reprogrammable CMOS PAL Device |

| PALC22V10B | Reprogrammable CMOS PAL Device |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PALC22V10-25WMB | 制造商:Cypress Semiconductor 功能描述: |

| PALC22V10-30DM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| PALC22V10-30HMB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

| PALC22V1030LMB | 制造商:CYPRESS 功能描述:IC |

| PALC22V10-30LMB | 制造商:CYPRESS 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。