- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224662 > PACE1754-20PGMB (PYRAMID SEMICONDUCTOR CORP) SPECIALTY MICROPROCESSOR CIRCUIT, CPGA68 PDF資料下載

參數(shù)資料

| 型號(hào): | PACE1754-20PGMB |

| 廠商: | PYRAMID SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, CPGA68 |

| 封裝: | PGA-68 |

| 文件頁數(shù): | 2/16頁 |

| 文件大?。?/td> | 143K |

| 代理商: | PACE1754-20PGMB |

PACE1754/SOS

Page 10 of 16

Document # MICRO-9 REV B

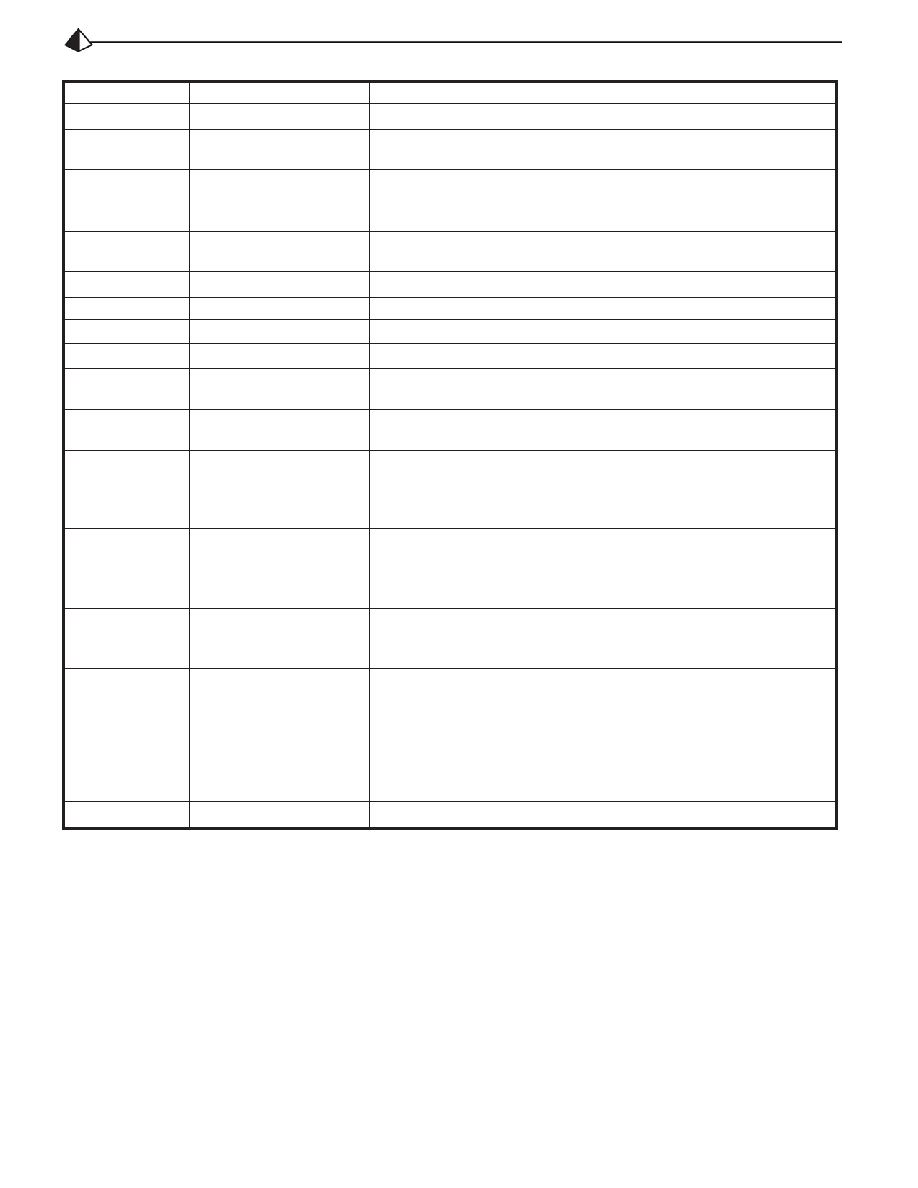

PIN FUNCTIONS

Symbol

Name

Description

CPU CLK

CPU Clock

A single-phase input clock signal (0-40MHz, 40% to 60% duty cycle.)

STRBA

Strobe Address

An active HIGH input which latches the contents of IB(0:15) into the

address latches.

STRBD

Strobe Data

An active LOW input which is used for writing or reading data to or

from the device and also to produce the external memory and I/O

strobes.

TIMER CLK

Timer Clock

A 100KHz output (fixed frequency) based on the programmed

operating frequency of the CPU clock.

MEMW

Memory Write Strobe

An active LOW output produced in memory write cycles.

MEMR

Memory Read Strobe

An active LOW output produced in memory read cycles.

IOW

I/O Write Strobe

An active LOW output produced in output write cycles.

IOR

I/O Read Strobe

An active LOW output produced in input read cycles.

INTA

Interrupt Acknowledge

An active LOW output produced after any interrupt, corresponding to

Strobe

an output write to address 1000 (hex).

SCR EN

System Configuration

An active LOW output (in 64 pin only) produced any time an input

read from address 8410 (hex), read system configuration is executed.

STRB EN

Strobe Enable

An active LOW input, enabling the active state of the address outputs

and the

MEMR, MEMQ, IOR, and IOW outputs. When at a logic "1"

(if enabled by bits EST, EAD of the control register) it will

correspondingly enable the three-state state of the above signals.

IB0 - IB15

Information Bus (0:15)

A bi-directional time multiplexed bus. It is an input during the

address phase of any bus cycle and also during the data phase

when writing. It is an output during the data phase when reading

from the device.

IB16

Information Bus (16)

A bi-directional line. It is an output during write cycles and an input

during read cycles. It is used to implement the parity function at the

system level.

A(0:1)/

Address Bus (0:15)

An active HIGH output bus. Contains the address of the current bus

EX AD(0:1),

cycle as latched by the end of STRBA. In system configurations

A(2:15)

including the MMU function, the only active lines during memory are

A(4:15). In this case, A(2:3) are high impedance (don't care) and

A(0:1) turn into inputs called Extended Addresses, EXT ADR (0:1).

In this case, these two lines supplied by the MMU, will be used to

operate the programmable ready generation during bus cycles.

M/

IO

Memory I/O

An input qualifier indicating the nature of the current bus cycle.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PAL16R8ANC | Progammable Array Logic Series 24 (PAL Series 24) |

| PAL16R8AVC | Progammable Array Logic Series 24 (PAL Series 24) |

| PAL18C1AN | Progammable Array Logic Series 24 (PAL Series 24) |

| PAL18C1ANC | Progammable Array Logic Series 24 (PAL Series 24) |

| PAL18C1ANM | Progammable Array Logic Series 24 (PAL Series 24) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PACE1757M | 制造商:PYRAMID 制造商全稱:Pyramid Semiconductor Corporation 功能描述:COMPLETE EMBEDDED CPU SUBSYSTEM |

| PACE1757ME | 制造商:PYRAMID 制造商全稱:Pyramid Semiconductor Corporation 功能描述:COMPLETE EMBEDDED CPU SUBSYSTEM |

| PA-CF07 | 制造商:Stellar Labs Power 功能描述:Pansonic ToughBook Replacement Laptop Battery |

| PA-CF18 | 制造商:Stellar Labs Power 功能描述:Panasonic ToughBook Replacement Laptop Battery |

| PA-CF29 | 制造商:Stellar Labs Power 功能描述:Pansonic ToughBook Replacement Laptop Battery |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。