- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367740 > P89C51RC2HXX (NXP Semiconductors N.V.) 80C51 8-bit Flash microcontroller family PDF資料下載

參數(shù)資料

| 型號: | P89C51RC2HXX |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 8位微控制器 |

| 英文描述: | 80C51 8-bit Flash microcontroller family |

| 中文描述: | 80C51的8位閃存微控制器系列 |

| 文件頁數(shù): | 31/68頁 |

| 文件大?。?/td> | 404K |

| 代理商: | P89C51RC2HXX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Philips Semiconductors

Preliminary data

P89C51RA2/RB2/RC2/RD2xx

80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

2002 Jul 18

31

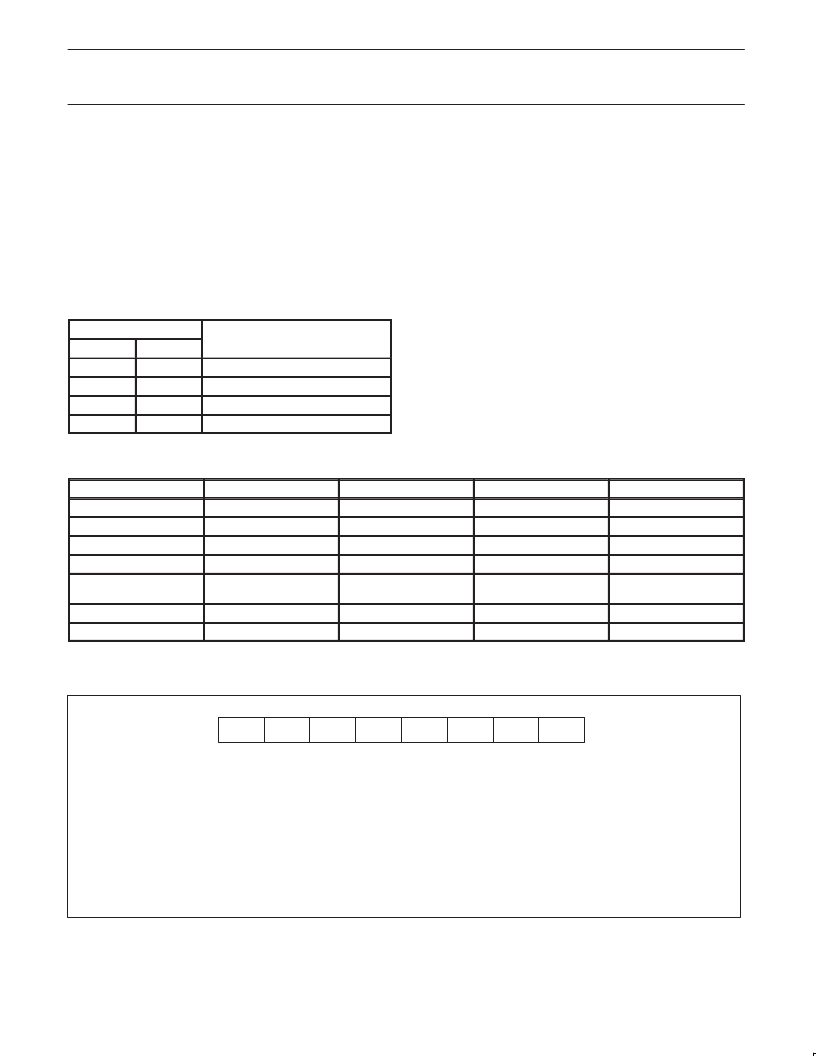

Interrupt Priority Structure

The P89C51RA2/RB2/RC2/RD2xx has a 7 source four-level

interrupt structure (see Table 7).

There are 3 SFRs associated with the four-level interrupt. They are

the IE, IP, and IPH. (See Figures 21, 22, and 23.) The IPH (Interrupt

Priority High) register makes the four-level interrupt structure

possible. The IPH is located at SFR address B7H. The structure of

the IPH register and a description of its bits is shown in Figure 23.

The function of the IPH SFR, when combined with the IP SFR,

determines the priority of each interrupt. The priority of each

interrupt is determined as shown in the following table:

PRIORITY BITS

INTERRUPT PRIORITY LEVEL

IPH.x

IP.x

0

0

Level 0 (lowest priority)

0

1

Level 1

1

0

Level 2

1

1

Level 3 (highest priority)

The priority scheme for servicing the interrupts is the same as that

for the 80C51, except there are four interrupt levels rather than two

as on the 80C51. An interrupt will be serviced as long as an interrupt

of equal or higher priority is not already being serviced. If an

interrupt of equal or higher level priority is being serviced, the new

interrupt will wait until it is finished before being serviced. If a lower

priority level interrupt is being serviced, it will be stopped and the

new interrupt serviced. When the new interrupt is finished, the lower

priority level interrupt that was stopped will be completed.

Table 7.

Interrupt Table

SOURCE

POLLING PRIORITY

REQUEST BITS

HARDWARE CLEAR

N (L)

1

VECTOR ADDRESS

X0

1

IE0

Y (T)

2

03H

T0

2

TP0

Y

0BH

X1

3

IE1

N (L)

Y (T)

13H

T1

4

TF1

Y

1BH

PCA

5

CF, CCFn

n = 0–4

N

33H

SP

6

RI, TI

N

23H

T2

7

TF2, EXF2

N

2BH

NOTES:

1. L = Level activated

2. T = Transition activated

EX0

IE (0A8H)

Enable Bit = 1 enables the interrupt.

Enable Bit = 0 disables it.

BIT

IE.7

SYMBOL

EA

FUNCTION

Global disable bit. If EA = 0, all interrupts are disabled. If EA = 1, each interrupt can be individually

enabled or disabled by setting or clearing its enable bit.

PCA interrupt enable bit

Timer 2 interrupt enable bit.

Serial Port interrupt enable bit.

Timer 1 interrupt enable bit.

External interrupt 1 enable bit.

Timer 0 interrupt enable bit.

External interrupt 0 enable bit.

IE.6

IE.5

IE.4

IE.3

IE.2

IE.1

IE.0

EC

ET2

ES

ET1

EX1

ET0

EX0

SU01290

ET0

EX1

ET1

ES

ET2

EC

EA

0

1

2

3

4

5

6

7

Figure 21. IE Registers

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P89C51UBPN | 80C51 8-bit microcontroller family 4K/8K/16K/32K Flash |

| P89C51UBAA-T | 8-BIT MICROCONTROLLER |

| P89C51BA | MICROCONTROLLER|8-BIT|8051 CPU|CMOS|LDCC|44PIN|PLASTIC |

| P89C51BBD | MICROCONTROLLER|8-BIT|8051 CPU|CMOS|QFP|44PIN|PLASTIC |

| P89C51BP | MICROCONTROLLER|8-BIT|8051 CPU|CMOS|DIP|40PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P89C51RCIN | 制造商: 功能描述: 制造商:NA 功能描述: 制造商:PHILS 功能描述: 制造商:undefined 功能描述: |

| P89C51RD+ | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit Flash microcontroller family 32K/64K ISP FLASH with 512.1K RAM |

| P89C51RD+IA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 8-bit Flash microcontroller family 32K/64K ISP FLASH with 512.1K RAM |

| P89C51RD+IA-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P89C51RD+IB | 制造商:NXP Semiconductors 功能描述: 制造商:Philips Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。