- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367723 > P87C575EHAA (NXP SEMICONDUCTORS) 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer PDF資料下載

參數(shù)資料

| 型號: | P87C575EHAA |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer |

| 中文描述: | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, MO-047AC, SOT-187-2, LCC-44 |

| 文件頁數(shù): | 15/40頁 |

| 文件大?。?/td> | 383K |

| 代理商: | P87C575EHAA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

Philips Semiconductors

Product specification

80C575/83C575/

87C575

80C51 8-bit microcontroller family

8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer

1998 May 01

15

CF

CR

CCF4

CCF3

CCF2

CCF1

CCF0

––

CCON

(D8H)

––

ECOMn

CAPPn

CAPNn

MATn

TOGn

PWMn

ECCFn

CCAPMn, n: 0..4

(DAH – DEH)

CH

CL

CCAPnH

CCAPnL

PCA INTERRUPT

PCA TIMER/COUNTER

1

0

0

0

16–BIT COMPARATOR

(TO CCFn)

WRITE TO

CCAPnH

RESET

WRITE TO

CCAPnL

0

1

ENABLE

CEXn

TOGGLE

MATCH

SU00751

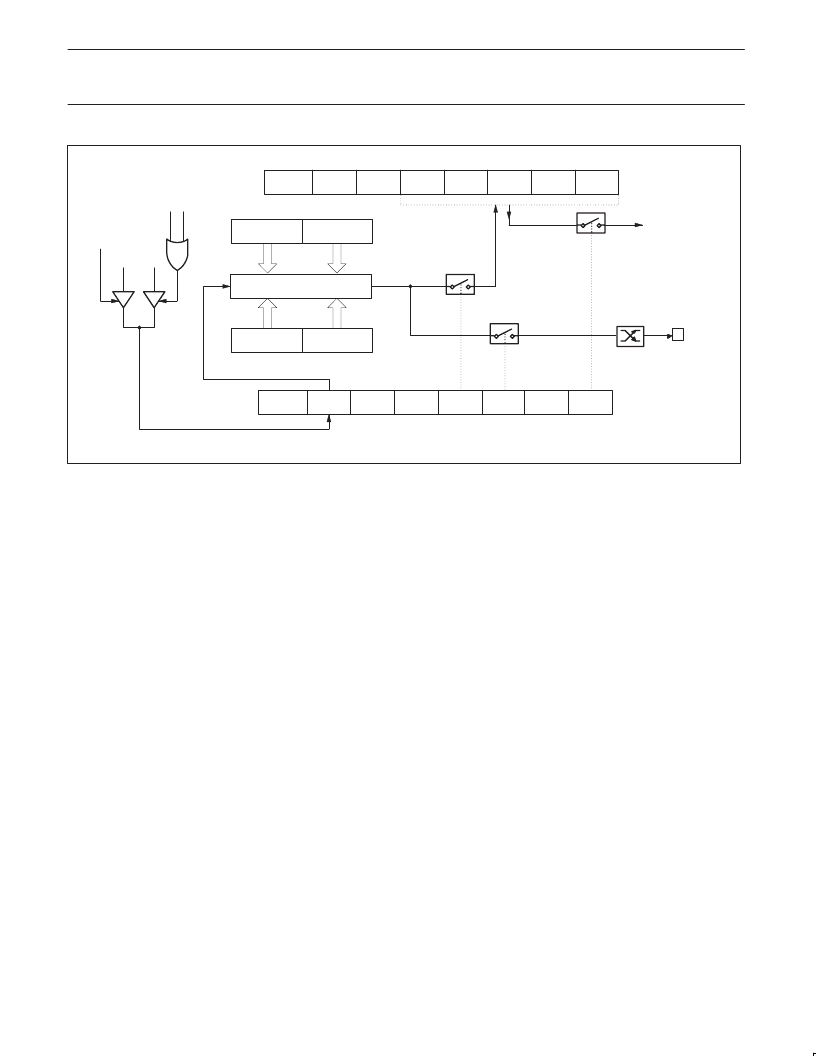

Figure 11. PCA High Speed Output Mode

Pulse Width Modulator Mode

All of the PCA modules can be used as PWM

outputs. Figure 12 shows the PWM function.

The frequency of the output depends on the

source for the PCA timer. All of the modules

will have the same frequency of output

because they all share the PCA timer. The

duty cycle of each module is independently

variable using the module’s capture register

CCAPLn. When the value of the PCA CL

SFR is less than the value in the module’s

CCAPLn SFR the output will be low, when it

is equal to or greater than the output will be

high. When CL overflows from FF to 00,

CCAPLn is reloaded with the value in

CCAPHn. the allows updating the PWM

without glitches. The PWM and ECOM bits in

the module’s CCAPMn register must be set

to enable the PWM mode.

WATCHDOG TIMER

The watchdog timer is not directly loadable

by the user. Instead, the value to be loaded

into the main timer is held in an autoload

register or is part of the mask ROM

programming. In order to cause the main

timer to be loaded with the appropriate value,

a special sequence of software action must

take place. This operation is referred to as

feeding the watchdog timer.

To feed the watchdog, two instructions must

be sequentially executed successfully. No

intervening instruction fetches are allowed,

so interrupts should be disabled before

feeding the watchdog. The instructions

should move A5H to the WFEED1 register

and then 5AH to the WFEED2 register. If

WFEED1 is correctly loaded and WFEED2 is

not correctly loaded, then an immediate

underflow will occur.

The watchdog timer subsystem has two

modes of operation. Its principal function is a

watchdog timer. In this mode it protects the

system from incorrect code execution by

causing a system reset when the watchdog

timer underflows as a result of a failure of

software to feed the timer prior to the timer

reaching its terminal count. If the user does

not employ the watchdog function, the

watchdog subsystem can be used as a timer.

In this mode, reaching the terminal count sets

a flag. In most other respects, the timer mode

possesses the characteristics of the

watchdog mode. This is done to protect the

integrity of the watchdog function.

The watchdog timer subsystem consists of a

prescaler and a main counter. The prescaler

has 8 selectable taps off the final stages and

the output of a selected tap provides the

clock to the main counter. The main counter

is the section that is loaded as a result of the

software feeding the watchdog and it is the

section that causes the system reset

(watchdog mode) or time-out flag to be set

(timer mode) if allowed to reach its terminal

count.

Programming the Watchdog Timer

Both the EPROM and ROM devices have a

set of SFRs for holding the watchdog

autoload values and the control bits. The

watchdog time-out flag is present in the

watchdog control register and operates the

same in all versions. In the EPROM device,

the watchdog parameters (autoload value

and control) are always taken from the SFRs.

In the ROM device, the watchdog parameters

can be mask programmed or taken from the

SFRs. The selection to take the watchdog

parameters from the SFRs or from the mask

programmed values is controlled by EA

(external access). When EA is high (internal

ROM access), the watchdog parameters are

taken from the mask programmed values. If

the watchdog is mask programmed to the

timer mode, then the autoload values and the

pre-scaler taps are taken from the SFRs.

When EA is low (external access), the

watchdog parameters are taken from the

SFRs. The user should be able to leave code

in his program which initializes the watchdog

SFRs even though he has migrated to the

mask ROM part. This allows no code

changes from EPROM prototyping to ROM

coded production parts.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C575EBPN | 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer |

| P87C575EBPN | 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer |

| P80C575EBAA | 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer |

| P83C575EBAA | 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer |

| P87C575EBAA | 80C51 8-bit microcontroller family 8K/256 OTP/ROM/ROMless, 4 comparator, failure detect circuitry, watchdog timer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P87C575EHAA-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P87C575EHFA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| P87C575EHKA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| P87C575EHN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| P87C576EBA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。