- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄367732 > P83C750EBAA (NXP SEMICONDUCTORS) 80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count PDF資料下載

參數(shù)資料

| 型號(hào): | P83C750EBAA |

| 廠(chǎng)商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC28 |

| 封裝: | PEDESTAL, PLASTIC, MO-047AB, SOT-261-3, LCC-28 |

| 文件頁(yè)數(shù): | 10/16頁(yè) |

| 文件大?。?/td> | 158K |

| 代理商: | P83C750EBAA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

Philips Semiconductors

Product specification

83C750/87C750

80C51 8-bit microcontroller family

1K/64 OTP/ROM, low pin count

1998 May 01

10

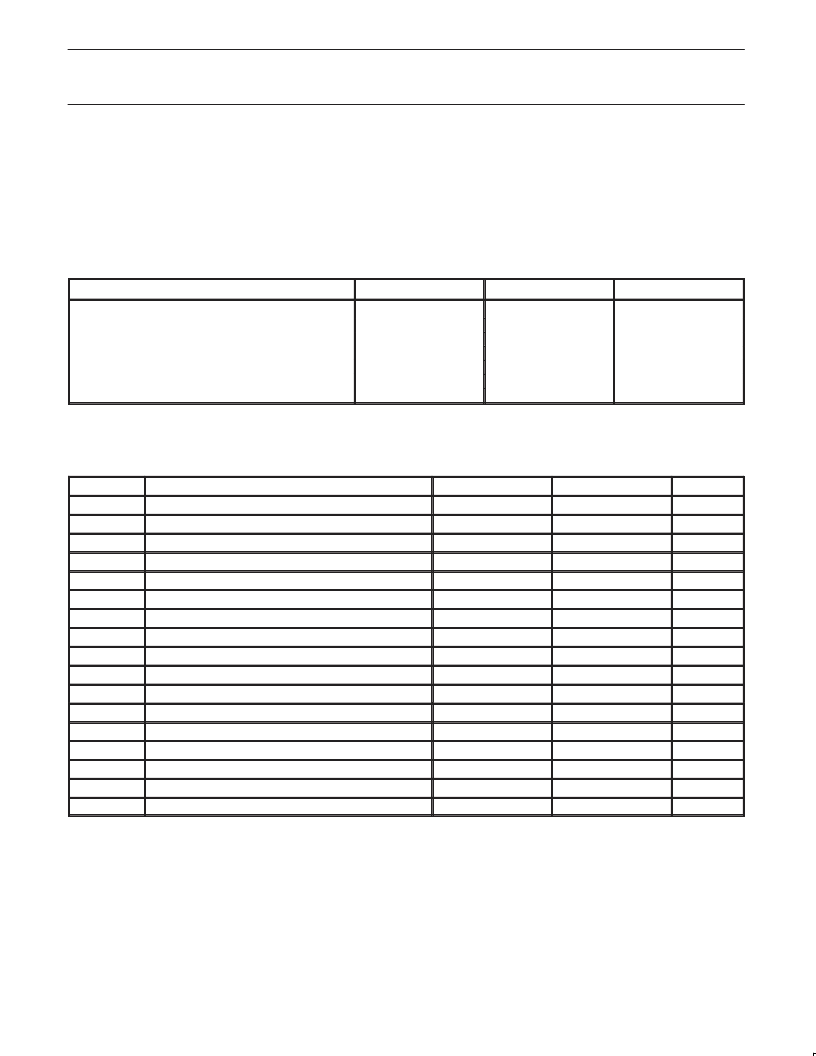

Programming and Verifying Security Bits

Security bits are programmed employing the same techniques used

to program the USER EPROM and KEY arrays using serial data

streams and logic levels on port pins indicated in Table 3. When

programming either security bit, it is not necessary to provide

address or data information to the 87C750 on ports 1 and 3.

Verification occurs in a similar manner using the RESET serial

stream shown in Table 3. Port 3 is not required to be driven and the

results of the verify operation will appear on ports 1.6 and 1.7.

Ports 1.7 contains the security bit 1 data and is a logical one if

programmed and a logical zero if not programmed. Likewise, P1.6

contains the security bit 2 data and is a logical one if programmed

and a logical zero if not programmed.

Table 3. Implementing Program/Verify Modes

OPERATION

SERIAL CODE

P0.1 (PGM/)

P0.2 (V

PP

)

Program user EPROM

Verify user EPROM

Program key EPROM

Verify key EPROM

Program security bit 1

Program security bit 2

Verify security bits

NOTE:

1. Pulsed from V

IH

to V

IL

and returned to V

IH

.

296H

296H

292H

292H

29AH

298H

29AH

–

1

V

IH

–

1

V

IH

–

1

–

1

V

IH

V

PP

V

IH

V

PP

V

IH

V

PP

V

PP

V

IH

EPROM PROGRAMMING AND VERIFICATION

T

amb

= 21

°

C to +27

°

C, V

CC

= 5V

±

10%, V

SS

= 0V

SYMBOL

PARAMETER

MIN

MAX

UNIT

1/t

CLCL

t

AVGL1

t

GHAX

t

DVGL

t

DVGL

t

GHDX

t

SHGL

t

GHSL

t

GLGH

t

AVQV2

t

GHGL

t

SYNL

t

SYNH

t

MASEL

t

MAHLD

t

HASET

t

ADSTA

NOTES:

1. Address should be valid at least 24t

CLCL

before the rising edge of P0.2 (V

PP

).

2. For a pure verify mode, i.e., no program mode in between, t

AVQV

is 14t

CLCL

maximum.

Oscillator/clock frequency

1.2

6

MHz

Address setup to P0.1 (PROG–) low

10

μ

s + 24t

CLCL

48t

CLCL

38t

CLCL

38t

CLCL

36t

CLCL

10

Address hold after P0.1 (PROG–) high

Data setup to P0.1 (PROG–) low

Data setup to P0.1 (PROG–) low

Data hold after P0.1 (PROG–) high

V

PP

setup to P0.1 (PROG–) low

V

PP

hold after P0.1 (PROG–)

P0.1 (PROG–) width

μ

s

μ

s

μ

s

10

90

110

V

PP

low (V

CC

) to data valid

P0.1 (PROG–) high to P0.1 (PROG–) low

48t

CLCL

10

μ

s

P0.0 (sync pulse) low

4t

CLCL

8t

CLCL

13t

CLCL

2t

CLCL

13t

CLCL

P0.0 (sync pulse) high

ASEL high time

Address hold time

Address setup to ASEL

Low address to valid data

48t

CLCL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P87C750EBAA | 0.5MM FFC JUMPER |

| P87C750EFPN | 80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

| P87C750EBPN | 80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

| P83C750EBPN | 16-Bit Buffers/Drivers with 3-State Outputs 48-SSOP -40 to 85 |

| P83C750EFAA | 128K X 16 BIT, 90 NS, 0-70 C, CMOS EPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C750EBDDB | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

| P83C750EBPN | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

| P83C750EFAA | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

| P83C750EFD | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

| P83C750EFPN | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:80C51 8-bit microcontroller family 1K/64 OTP ROM, low pin count |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。