- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369944 > P83C524IFP (NXP SEMICONDUCTORS) 8-bit microcontrollers PDF資料下載

參數(shù)資料

| 型號(hào): | P83C524IFP |

| 廠(chǎng)商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-bit microcontrollers |

| 中文描述: | 8-BIT, MROM, 24 MHz, MICROCONTROLLER, PDIP40 |

| 封裝: | 0.600 INCH, PLASTIC, DIP-40 |

| 文件頁(yè)數(shù): | 37/76頁(yè) |

| 文件大小: | 400K |

| 代理商: | P83C524IFP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

1997 Dec 15

37

Philips Semiconductors

Product specification

8-bit microcontrollers

P83C524; P80C528; P83C528

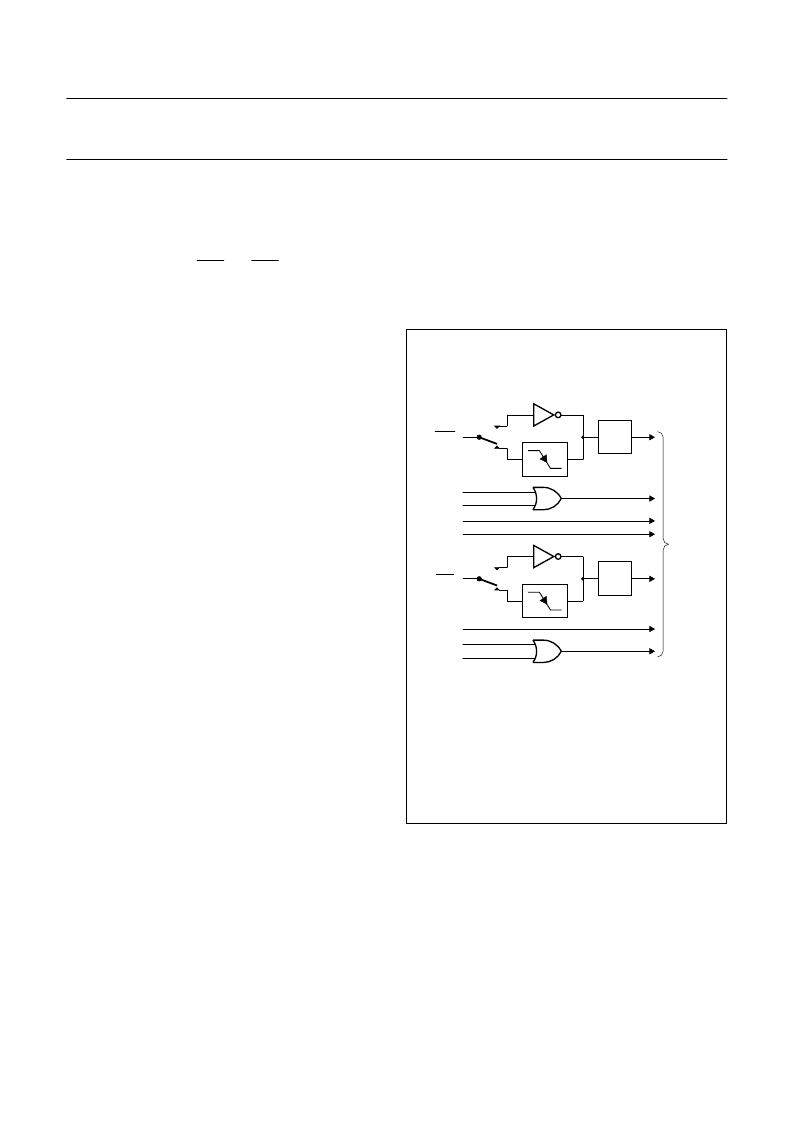

14 INTERRUPT SYSTEM

The P83C528 contains the same interrupt structure as the

PCB80C51BH, but with a seven-source interrupt structure

with two priority levels (see Fig.19).

The External Interrupts INT0 and INT1 can each be either

level-activated or transition-activated, depending on bits

IT0 and IT1 in TCON SFR. The flags that actually generate

these interrupts are bits IE0 and IE1 in TCON. When an

external interrupt is generated, the corresponding request

flag is cleared by the hardware when the service routine is

vectored to, only if the interrupt was transition-activated. If

the interrupt was level-activated then the interrupt request

flag remains set until the external interrupt pin INTx goes

high.

The Timer 0 and Timer 1 Interrupts are generated by TF0

and TF1, which are set by a rollover in their respective

timer/counter register (except for Timer 0 in Mode 3 of the

serial interface). When a Timer interrupt is generated, the

flag that generated it is cleared by the on-chip hardware

when the service routine is vectored to.

The Serial Port Interrupt is generated by the logical 'OR' of

RI and TI. Neither of these flags is cleared by hardware.

The service routine will normally have to determine

whether it was RI or TI that generated the interrupt, and the

bit will have to be cleared by software.

The Timer 2 Interrupt is generated by the logical OR of TF2

and EXF2. Neither of these flags is cleared by hardware.

In fact the service routine may have to determine whether

it was TF2 or EXF2 that generated the interrupt, and the bit

will have to be cleared by software.

An additional (third) external interrupt is available, if Timer

2 is not used as timer/counter or if Timer 2 is used in baud

rate generator mode. That external interrupt 2 is falling

edge triggered. It shares the Timer 2 interrupt vector,

interrupt enable and interrupt priority bits. If bit

T2CON.3/EXEN2 = 1, a HIGH-to-LOW transition at pin

P1.1/T2EX sets the interrupt request flag T2CON.6/EXF2

and can be used to generate an external interrupt.

The I

2

C interrupt is generated by SI in S1INT. This flag has

to be cleared by software. All of the bits that generate

interrupts can be set or cleared by software, with the same

result as though they had been set or cleared by hardware,

with the exception of the I

2

C interrupt request flag SI,

which cannot be set by software. That is, interrupts can be

generated or pending interrupts can be cancelled in

software.

Fig.19 P83C528 Interrupt Sources.

handbook, halfpage

MBC481 - 1

IE1

0

1

IE0

0

1

interrupt

sources

INT0

TF2

EXF2

SI

TF0

INT1

TF1

TI

RI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C524IBP | 8-bit microcontrollers |

| P83C524 | 8-bit microcontrollers |

| P83C524EBA | 8-bit microcontrollers |

| P83C524EBB | 8-bit microcontrollers |

| P83C524EBP | 8-bit microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C528 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:8-bit microcontrollers |

| P83C528BBA | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

| P83C528BBP | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

| P83C528BHA | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

| P83C528BHP | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。