- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369944 > P83C524EFA (NXP SEMICONDUCTORS) CONN, JACK MODULAR 90DEG 4P 4C PDF資料下載

參數(shù)資料

| 型號(hào): | P83C524EFA |

| 廠(chǎng)商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | CONN, JACK MODULAR 90DEG 4P 4C |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁(yè)數(shù): | 36/76頁(yè) |

| 文件大?。?/td> | 400K |

| 代理商: | P83C524EFA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

1997 Dec 15

36

Philips Semiconductors

Product specification

8-bit microcontrollers

P83C524; P80C528; P83C528

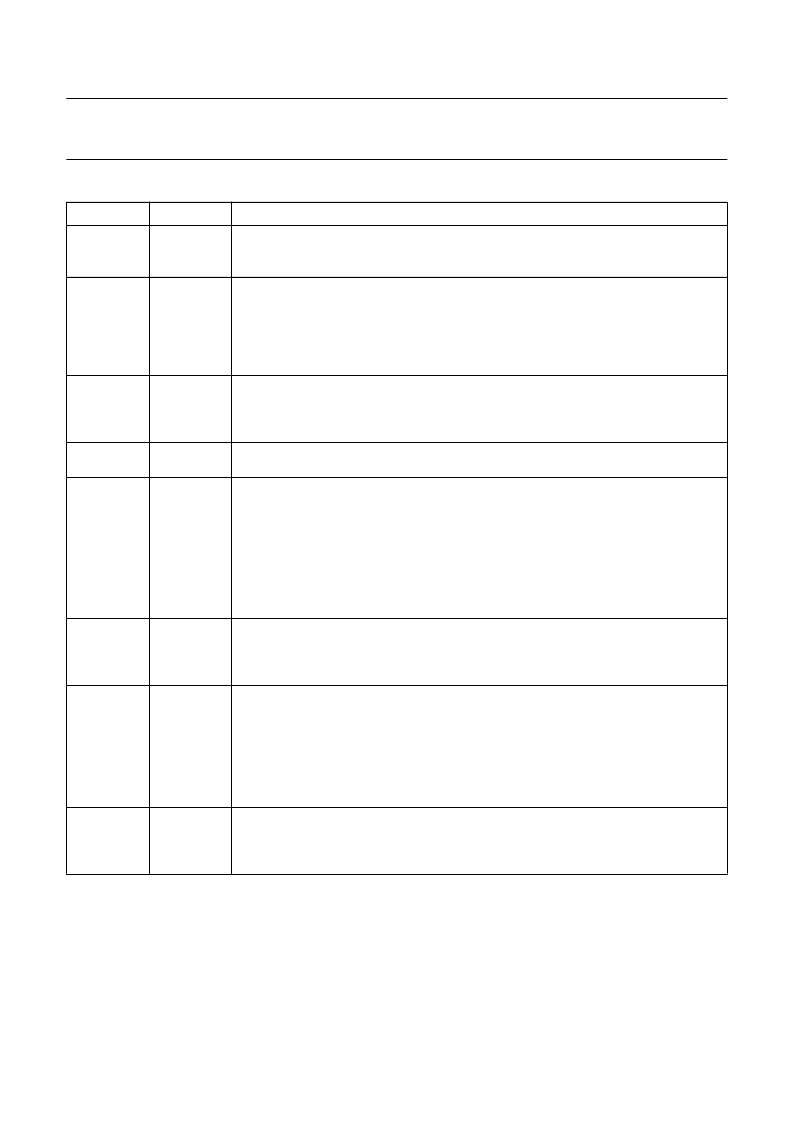

Table 20

Description of the S1SCS bits

BIT

SYMBOL

FUNCTION

7

SDO/SDI

Serial Data Output and the filtered Serial Data Input

. SDI data is latched on the rising

edge of the filtered serial clock. S1SCS.7 accesses the same memory locations as

S1BIT.7. Access of the data bit via S1SCS will not start an auto-clock pulse.

Serial Clock Output and the filtered Serial Clock Input

. Serial clock output SCO is

'OR-ed' with the auto-clock. If SCO = 1 the auto-clock output is inhibited. The internal

clock stretching logic and external devices can pull the SCL line LOW. If the auto-clock

is not used, the SCL line has to be controlled by setting SCO = 1, waiting for CLH = 1

and setting SCO = 0 after the specified SCL HIGH time. (Because of the input filter,

CLH will be set at least 8 XTAL clock periods after the SCL LOW-to-HIGH transition.)

Serial Clock LOW-to-HIGH transition flag

: set with a rising edge of the filtered serial

clock. CLH = 1 indicates that, since the last CLH reset, a new valid data bit has been

latched in SDI. CLH can be reset by writing a 0 to S1SCS.5 or by a read/write of S1BIT.

Clearing CLH also clears RBF and WBF.

Bus Busy flag

: indicating that there has been a START condition that was not yet

followed by a STOP condition.

Read Bit Finished flag

: indicating a successful bit read.

RBF = 1 implies the following conditions:

CLH = 1: SCL had a rising edge

SCI = 0: the SCL pulse has finished

SI = 0: no START condition occurred

BB = 1: no STOP condition occurred

The RBF flag can be cleared by clearing the CLH flag.

Write Bit Finished flag

: indicating a successful bit write. The same conditions as for

RBF are true and also no 'arbitration loss' condition occurred. Arbitration is lost if a

1 data bit in SDO was over-ruled on SDA by an external device. The WBF flag can be

cleared by clearing the CLH flag.

STRetch control flag

. STR = 1 enables stretching of all SCL LOW periods. This allows

the processor in I

2

C slave mode to react on a fast master. The STR flag remains set

until cleared by writing a 0 to S1SCS.1.

6

SCO/SCI

5

CLH

4

BB

3

RBF

2

WBF

1

STR

The STretch (ST)

flag (not readable) pulls the serial clock LOW while ST = 1. The ST

flag is set on the falling edge of the filtered serial clock if STR = 1. It is also set after

reception of a START condition, regardless of the STR contents. ST is cleared with a

read or write of S1BIT.

ENable Serial I/O flag

. ENS = 1 enables the START detection and clock stretching

logic. ENS = 0 can be used to switch off the I

2

C-bus hardware. Note that the SDO and

SCO control flags must be set to 1 before ENS is set to avoid pulling SCL or SDA lines

to 0.

0

ENS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C524EFP | CONN HEADER 12POS SGL PCB 30GOLD |

| P83C524IBA | 8-bit microcontrollers |

| P83C524IBB | 8-bit microcontrollers |

| P83C524IFB | 8-bit microcontrollers |

| P83C524IFP | 8-bit microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C524EFB | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:8-bit microcontrollers |

| P83C524EFP | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:8-bit microcontrollers |

| P83C524FFA | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

| P83C524FFP | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

| P83C524FHA | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。