- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367736 > P80C528FBBB (NXP SEMICONDUCTORS) CMOS single-chip 8-bit microcontroller PDF資料下載

參數(shù)資料

| 型號: | P80C528FBBB |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CMOS single-chip 8-bit microcontroller |

| 中文描述: | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP44 |

| 文件頁數(shù): | 10/26頁 |

| 文件大?。?/td> | 447K |

| 代理商: | P80C528FBBB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

Philips Semiconductors

Product specification

80C528/83C528

CMOS single-chip 8-bit microcontrollers

1995 Feb 02

10

– setting Read Bit Finished (RBF) when the

SCL clock pulse has finished and Write Bit

Finished (WBF) if there is no arbitration

loss detected (i.e., SDA = 0 while SDO = 1)

– setting a serial clock Low-to-High detected

(CLH) flag

– setting a Bus Busy (BB) flag on a START

condition and clearing this flag on a STOP

condition

– releasing the SCL line and clearing the

CLH, RBF and WBF flags to resume

transfer of the next serial data bit

– generating an automatic clock if the single

bit data register S1BIT is used in master

mode.

The following functions must be done in

software:

– handling the I

2

C START interrupts

– converting serial to parallel data when

receiving

– converting parallel to serial data when

transmitting

– comparing the received slave address with

its own

– interpreting the acknowledge information

– guarding the I

2

C status if RBF or WBF = 0.

Additionally, if acting as master:

– generating START and STOP conditions

– handling bus arbitration

– generating serial clock pulses if S1BIT is

not used.

Three SFRs control the bit-level I

2

C interface:

S1INT, S1BIT and S1SCS.

INTERRUPT SYSTEM

The interrupt structure of the 8XC528 is the

same as that used in the 80C51, but includes

two additional interrupt sources: one for the

third timer/counter, T2, and one for the I

2

C

interface. The interrupt enable and interrupt

priority registers are IE and IP.

IE: Interrupt Enable Register

This register is located at address A8H. Refer

to Table 3.

IE SFR (A8H)

ET1

ES

ES1

ET2

EA

EX1

ET0

EX0

7

6

5

4

3

2

1

0

IP: Interrupt Priority Register

This register is located at address B8H. Refer

to Table 4.

IP SFR (B8H)

PT1

PS

PS1

PT2

–

PX1

PT0

PX0

7

6

5

4

3

2

1

0

The interrupt vector locations and the

interrupt priorities are:

Source

Vector

0003H

002BH

0053H

000BH

0013H

001BH

0023H

Priority within Level

Address

IE0

TF2+EXF2

SI (I

2

C)

TF0

IE1

TF1

R1+T1

Highest

Lowest

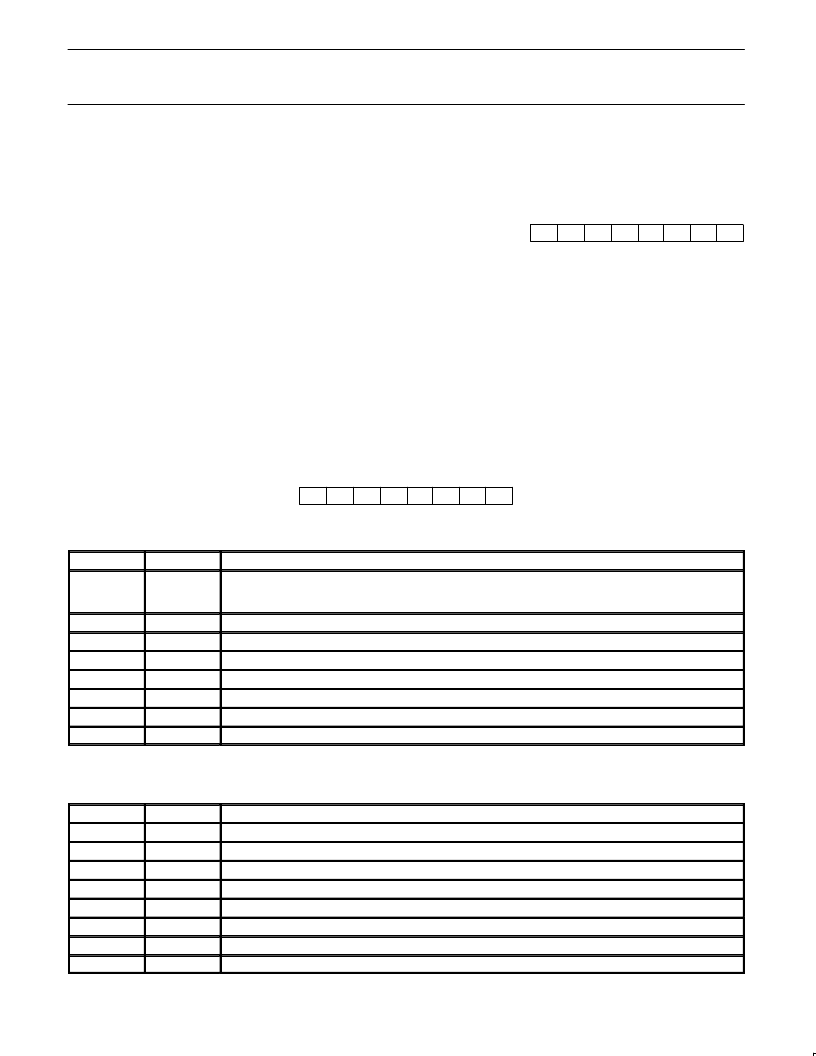

Table 3.

Description of IE Bits

MNEMONIC

BIT

FUNCTION

EA

IE.7

General enable/disable control:

0 =

NO

interrupt is enabled.

1 =

ANY

individually enabled interrupt will be accepted.

ES1

IE.6

Enable

bit-level I

2

C I/O

interrupt

Enable

Timer 2

interrupt

ET2

IE.5

ES

IE.4

Enable

Serial Port

interrupt

ET1

IE.3

Enable

Timer 1

interrupt

EX1

IE.2

Enable

External

interrupt 1

ET0

IE.1

Enable

Timer 0

interrupt

EX0

IE.0

Enable

External

interrupt 0

Table 4.

Description of IP Bits

MNEMONIC

BIT

FUNCTION

–

IP.7

Reserved.

Bit-level I

2

C

interrupt priority level

PS1

IP.6

PT2

IP.5

Timer 2

interrupt priority level

PS

IP.4

Serial Port

interrupt priority level

PT1

IP.3

Timer 1

interrupt priority level

PX1

IP.2

External Interrupt 1

priority level

PT0

IP.1

Timer 0

interrupt priority level

PX0

IP.0

External Interrupt 0

priority level

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C528FBBB | CMOS single-chip 8-bit microcontroller |

| P80C528FBPN | CMOS single-chip 8-bit microcontroller |

| P83C528FBPN | CMOS single-chip 8-bit microcontroller |

| P80C528FBB | CMOS single-chip 8-bit microcontroller |

| P83C528FBB | CMOS single-chip 8-bit microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P80C528FBP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller |

| P80C528FBPN | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller |

| P80C528FFA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller |

| P80C528FFAA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller |

| P80C528FFAA-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。