- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369942 > P80C151SB (INTEL CORP) HIGH-PERFORMANCE CHMOS MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | P80C151SB |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | HIGH-PERFORMANCE CHMOS MICROCONTROLLER |

| 中文描述: | 8-BIT, 16 MHz, MICROCONTROLLER, PDIP40 |

| 封裝: | PLASTIC, DIP-40 |

| 文件頁數(shù): | 9/33頁 |

| 文件大小: | 312K |

| 代理商: | P80C151SB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

8XC151SA/SB HIGH-PERFORMANCE CHMOS MICROCONTROLLER

SIGNAL DESCRIPTIONS

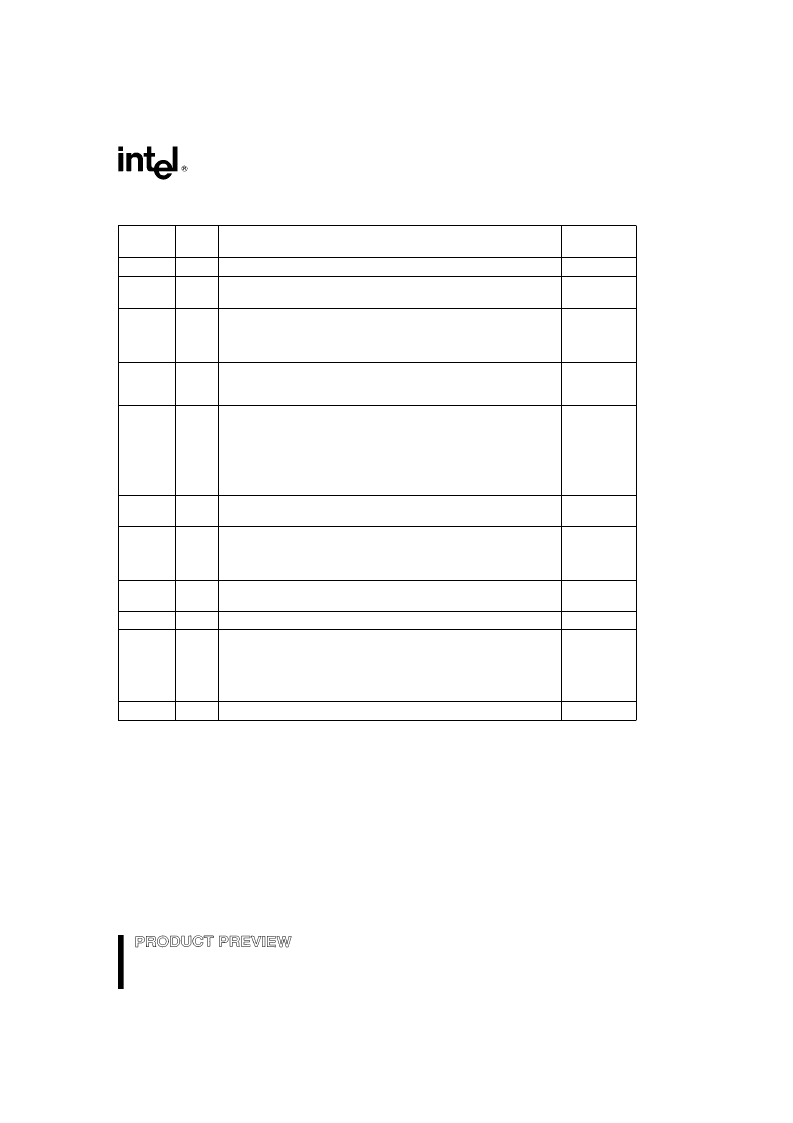

Table 7. Signal Descriptions

Signal

Name

Type

Description

Multiplexed

With

A15:8

2

O

Address Lines.

Upper address lines for the external bus.

P2.7:0

AD7:0

2

I/O

Address/Data Lines.

Multiplexed lower address lines and data lines

for external memory.

P0.7:0

ALE

O

Address Latch Enable.

ALE signals the start of an external bus

cycle and indicates that valid address information is available on lines

A15:8 and AD7:0. An external latch can use ALE to demultiplex the

address from the address/data bus.

PROG

Y

CEX4:0

I/O

Programmable Counter Array (PCA) Input/Output Pins.

These

are input signals for the PCA capture mode and output signals for the

PCA compare mode and PCA PWM mode.

P1.6:3

P1.7

EA

Y

I

External Access.

Directs program memory accesses to on-chip or

off-chip code memory. For EA

Y

e

0, all program memory accesses

are off-chip. For EA

Y

e

1, an access is to on-chip ROM/OTPROM if

the address is within the range of the on-chip ROM/OTPROM;

otherwise the access is off-chip. The value of EA

Y

is latched at

reset. For devices without on-chip ROM/OTPROM, EA

Y

must be

strapped to ground.

V

PP

ECI

I

PCA External Clock Input.

External clock input to the 16-bit PCA

timer.

P1.2

INT1:0

Y

I

External Interrupts 0 and 1.

These inputs set bits IE1:0 in the TCON

register. If bits IT1:0 in the TCON register are set, bits IE1:0 are set by

a falling edge on INT1

Y

/INT0

Y

. If bits INT1:0 are clear, bits IE1:0

are set by a low level on INT1:0

Y

.

P3.3:2

PROG

Y

I

Programming Pulse.

The programming pulse is applied to this pin

for programming the on-chip OTPROM.

ALE

P0.7:0

I/O

Port 0.

This is an 8-bit, open-drain, bidirectional I/O port.

AD7:0

P1.0

P1.1

P1.2

P1.7:3

I/O

Port 1.

This is an 8-bit, bidirectional I/O port with internal pullups.

T2

T2EX

ECI

CEX3:0

CEX4

P2.7:0

I/O

Port 2.

This is an 8-bit, bidirectional I/O port with internal pullups.

A15:8

2

The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration (compatible with

44-lead PLCC and 40-pin DIP MCS 51 microcontrollers). If the chip is configured for page-mode operation, port 0 carries

the lower address bits (A7:0), and port 2 carries the upper address bits (A15:8) and the data (D7:0).

9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C151SA | HIGH-PERFORMANCE CHMOS MICROCONTROLLER |

| P83C151SB | HIGH-PERFORMANCE CHMOS MICROCONTROLLER |

| P87C151SA | HIGH-PERFORMANCE CHMOS MICROCONTROLLER |

| P87C151SB | HIGH-PERFORMANCE CHMOS MICROCONTROLLER |

| P8XC151SA | HIGH-PERFORMANCE CHMOS MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P80C151SB16 | 制造商:Intel 功能描述: |

| P80C152A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P80C152JA | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:UNIVERSAL COMMUNICATION CONTROLLER 8-BIT MICROCONTROLLER |

| P80C152JA-1 | 制造商:INTELC 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| P80C152JC | 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。