- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369939 > P28F001BX-B150 (INTEL CORP) 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY PDF資料下載

參數(shù)資料

| 型號(hào): | P28F001BX-B150 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| 中文描述: | 128K X 8 FLASH 12V PROM, 150 ns, PDIP32 |

| 封裝: | 0.620 X 1.640 INCH, PLASTIC, DIP-32 |

| 文件頁數(shù): | 30/33頁 |

| 文件大小: | 436K |

| 代理商: | P28F001BX-B150 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁

28F001BX-T/28F001BX-B

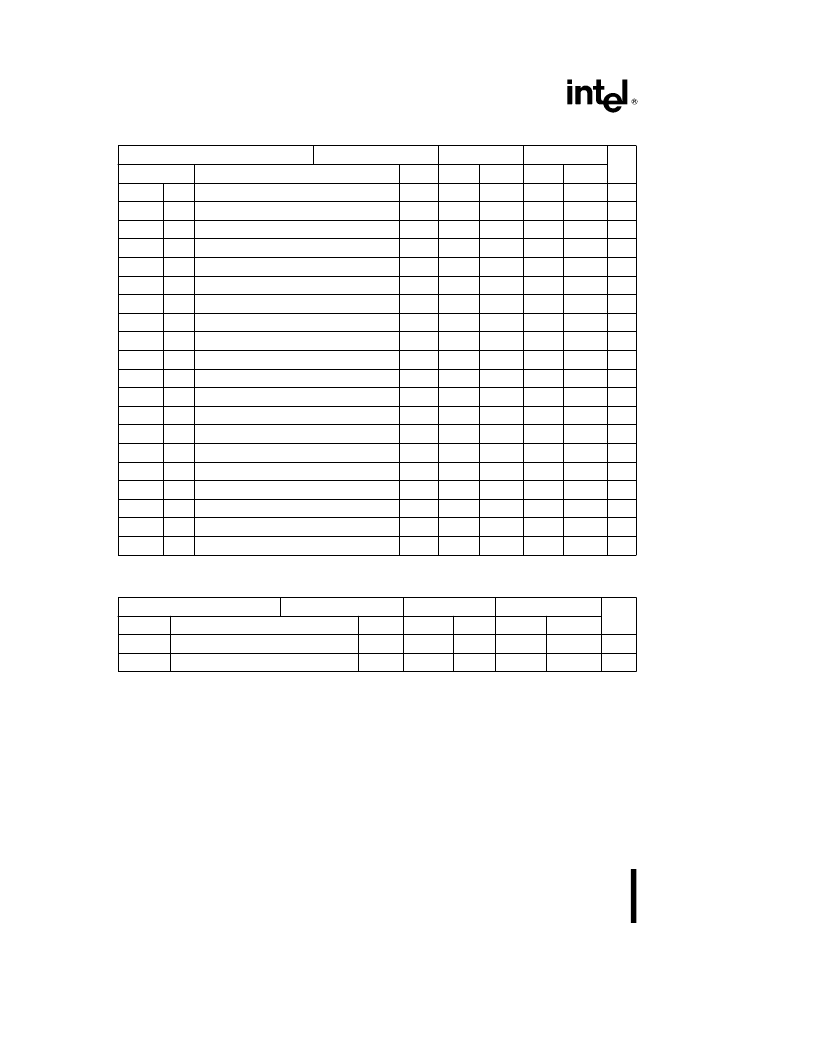

AC CHARACTERISTICS FOR CE

Y

-CONTROLLED WRITES

(1)

Versions

V

CC

g

10%

28F001BX-120

28F001BX-150

Unit

Symbol

Parameter

Notes

Min

Max

Min

Max

t

AVAV

t

WC

Write Cycle Time

120

150

ns

t

PHEL

t

PS

RP

Y

High Recovery to CE

Y

Going Low

2

480

480

ns

t

WLEL

t

WS

WE

Y

Setup to CE

Y

Going Low

0

0

ns

t

ELEH

t

CP

CE

Y

Pulse Width

70

70

ns

t

PHHEH

t

PHS

RP

Y

V

HH

Setup to CE

Y

Going High

V

PP

Setup to CE

Y

Going High

Address Setup to CE

Y

Going High

2

100

100

ns

t

VPEH

t

VPS

2

100

100

ns

t

AVEH

t

AS

3

50

50

ns

t

DVEH

t

DS

Data Setup to CE

Y

Going High

4

50

50

ns

t

EHDX

t

DH

Data Hold from CE

Y

High

10

10

ns

t

EHAX

t

AH

Address Hold from CE

Y

High

15

15

ns

t

EHWH

t

WH

WE

Y

Hold from CE

Y

High

0

0

ns

t

EHEL

t

EPH

CE

Y

Pulse Width High

25

25

ns

t

EHQV1

Duration of Programming Operation

5, 6

15

15

m

s

t

EHQV2

Duration of Erase Operation (Boot)

5, 6

1.3

1.3

sec

t

EHQV3

Duration of Erase Operation (Parameter)

5, 6

1.3

1.3

sec

t

EHQV4

Duration of Erase Operation (Main)

5, 6

3.0

3.0

sec

t

EHGL

Write Recovery before Read

0

0

m

s

t

QVVL

t

VPH

V

PP

Hold from Valid SRD

RP

Y

V

HH

Hold from Valid SRD

2, 5

0

0

ns

t

QVPH

t

PHH

2, 6

0

0

ns

t

PHBR

Boot-Block Relock Delay

2

100

100

ns

PROM Programmer Specifications

Versions

V

CC

g

10%

28F001BX-120

28F001BX-150

Unit

Symbol

Parameter

Notes

Min

Max

Min

Max

t

GHHEL

OE

Y

V

HH

Setup to CE

Y

Going Low

OE

Y

V

HH

Hold from CE

Y

High

2, 7

480

480

ns

t

EHGH

2, 7

480

480

ns

NOTES:

1. Chip-Enable Controlled Writes: Write operations are driven by the valid combination of CE

Y

and WE

Y

. In systems where

CE

Y

defines the write pulse width (within a longer WE

Y

timing waveform), all set-up, hold and inactive WE

Y

times should

be measured relative to the CE

Y

waveform.

2. Sampled, not 100% tested.

3. Refer to Table 3 for valid A

IN

for byte programming or block erasure.

4. Refer to Table 3 for valid D

IN

for byte programming or block erasure.

5. Program and erase durations are measured to completion (SR.7

e

1). V

PP

should be held at V

PPH

until determination of

program/erase success (SR.3/4/5

e

0).

6. For boot block programming and erasure, RP

Y

should be held at V

HH

until determination of program/erase success

(SR.3/4/5

e

0).

7. Alternate boot block access method.

30

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P28F001BX-B70 | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-B90 | DB9 MALE TO DB9 FEMALE AME |

| P28F002BC-T120 | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| P28F002BC-T80 | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| P28F512-150 | 512K(64Kx8)CMOS FLASH MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P28F001BX-B70 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-B90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-T120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-T150 | 制造商:Intel 功能描述:NOR Flash, 128K x 8, 32 Pin, Plastic, DIP |

| P28F001BX-T70 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。