- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224646 > OR2T08A-6BA84 (Electronic Theatre Controls, Inc.) Ceramic Chip Capacitors / MIL-PRF-55681; Capacitance [nom]: 30pF; Working Voltage (Vdc)[max]: 100V; Capacitance Tolerance: +/-5%; Dielectric: Multilayer Ceramic; Temperature Coefficient: C0G (NP0); Lead Style: Surface Mount Chip; Lead Dimensions: 1206; Termination: Solder Coated SnPb; Body Dimensions: 0.125" x 0.062" x 0.051"; Container: Bag; Features: MIL-PRF-55681: M Failure Rate PDF資料下載

參數(shù)資料

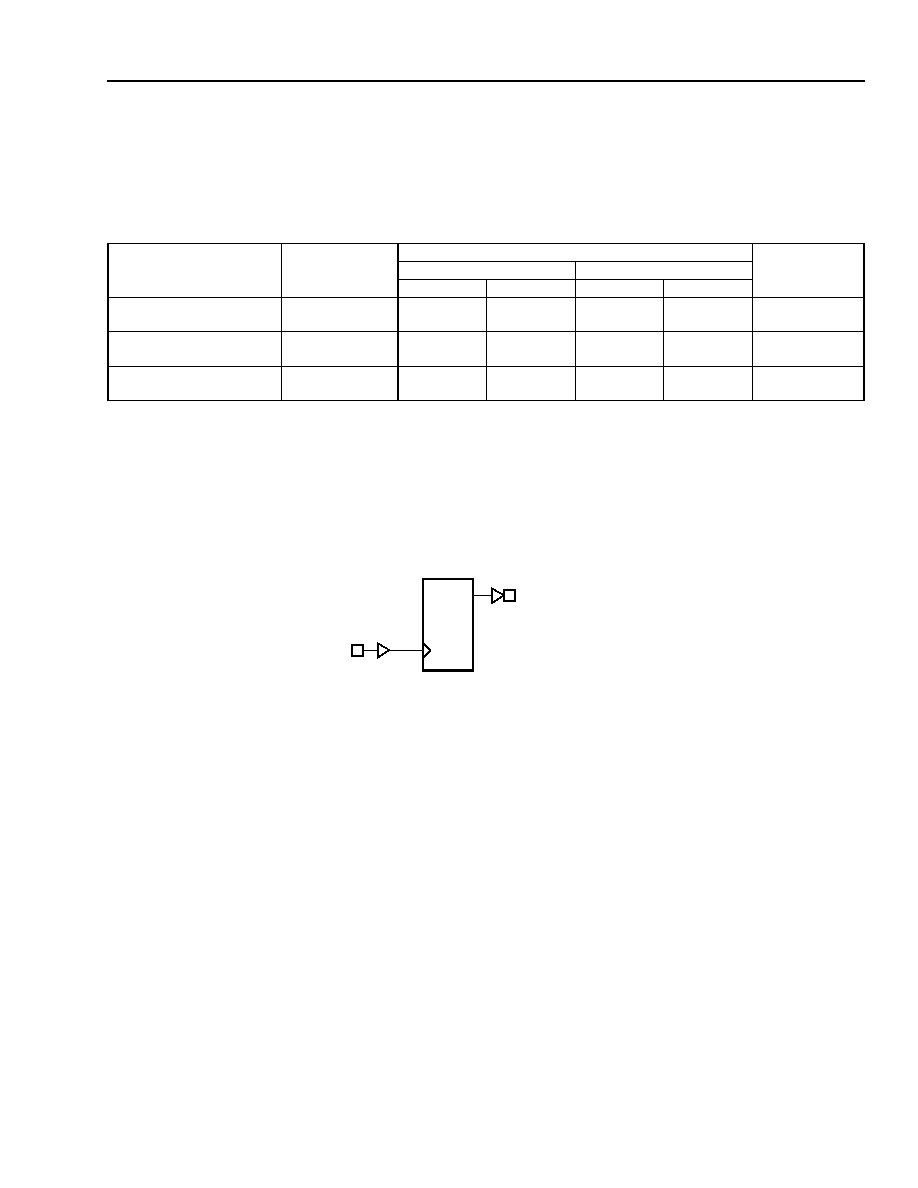

| 型號: | OR2T08A-6BA84 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Ceramic Chip Capacitors / MIL-PRF-55681; Capacitance [nom]: 30pF; Working Voltage (Vdc)[max]: 100V; Capacitance Tolerance: +/-5%; Dielectric: Multilayer Ceramic; Temperature Coefficient: C0G (NP0); Lead Style: Surface Mount Chip; Lead Dimensions: 1206; Termination: Solder Coated SnPb; Body Dimensions: 0.125" x 0.062" x 0.051"; Container: Bag; Features: MIL-PRF-55681: M Failure Rate |

| 中文描述: | 現(xiàn)場可編程門陣列 |

| 文件頁數(shù): | 61/192頁 |

| 文件大小: | 3148K |

| 代理商: | OR2T08A-6BA84 |