- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359236 > MU9C1640-40DC Content Addressable Memory PDF資料下載

參數(shù)資料

| 型號(hào): | MU9C1640-40DC |

| 英文描述: | Content Addressable Memory |

| 中文描述: | 內(nèi)容可尋址存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 16/28頁(yè) |

| 文件大?。?/td> | 246K |

| 代理商: | MU9C1640-40DC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

MU9C1480A/L Draft

Rev. 3.0 Draft

16

Address register must contain a unique value to prevent

bus contention. This process allows individual device

selection. The Page Address register initialization works

as follows: Writes to Page Address registers are only active

for devices with /FI LOW and /FF HIGH. At initialization,

all devices are empty, thus the top device in the string will

respond to a TCO PA instruction, and load its PA register.

To advance to the next device in the string, a Set Full Flag

(SFF) instruction is used, which is active only for the device

with /FI LOW and /FF HIGH. The SFF instruction changes

the first device’s /FF to LOW, although the device really is

empty, which allows the next device in the string to respond

to the TCO PA instruction and load its PA register. The

initialization proceeds through the chain in a similar manner

filling all the PA registers in turn. Each device must have a

unique Page Address value stored in its PA register, or

contention will result. After all the PA registers are filled,

the entire string is reset through the Control register, which

does not change the values stored in the individual PA

registers. After the reset, the Device Select registers usually

are set to FFFFH to enable operation in Case 1 of Table 5a

on page 12. The Control registers and the Segment Control

registers are then set to their normal operating values for

the application.

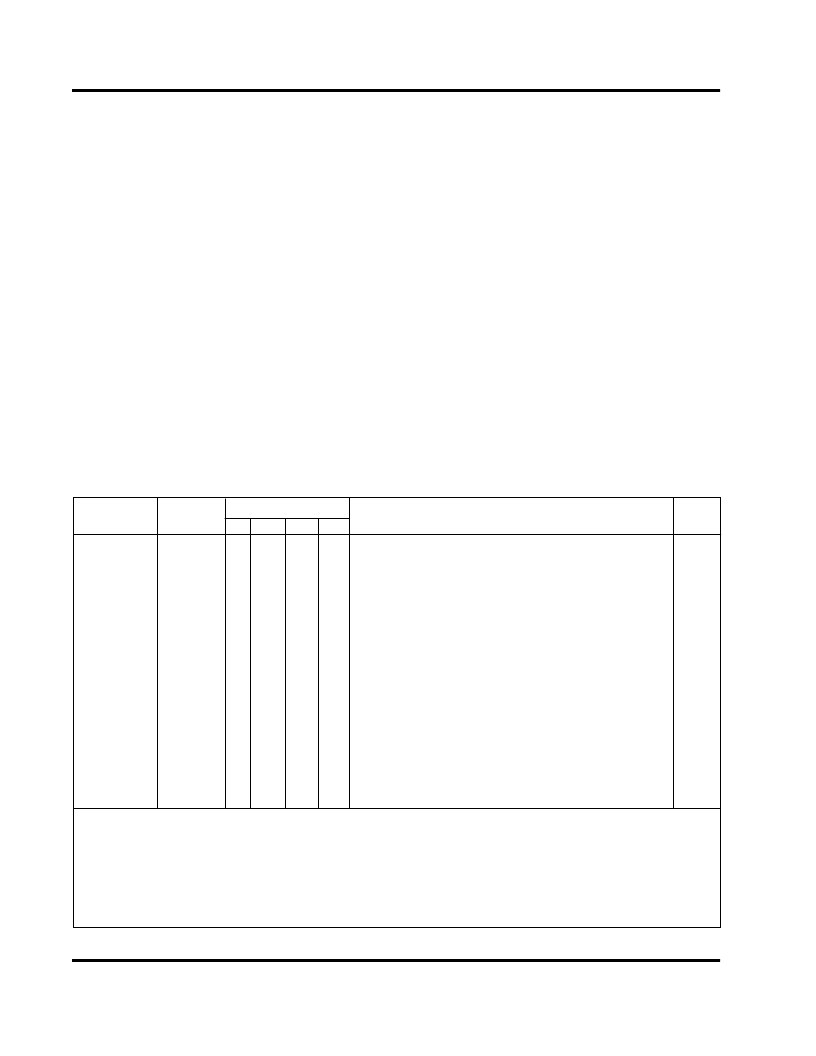

OPERATIONAL CHARACTERISTICS Continued

Vertically Cascaded System Initialization

T

able 6 shows an example of code that initializes a

daisy-chained string of LANCAM devices. The

initialization example shows how to set the Page Address

registers of each of the devices in the chain through the

use of the Set Full Flag instruction, and how the Control

registers and Segment counters of all the LANCAM devices

are set for a typical application. Each Page Address register

must contain a unique value (not FFFFH) to prevent bus

contention.

For typical daisy chain operation, data is loaded into the

Comparand registers of all the devices in a string

simultaneously by setting DS=FFFFH. Since reading is

prohibited when DS=FFFFH (except for the device with a

match), for a diagnostic operation you need to select a

specific device by setting DS=PA for the desired device to

be able to read from it. Refer to Tables 5a and 5b on page 12

for preconditions for reading and writing.

Initialization for a single LANCAM is similar. The Device

Select register in this case is usually set to equal the Page

Address register for normal operations. Also, the dedicated

/MA flag output can be used instead of /MF, allowing /EC

to be tied HIGH.

Cycle Type

Command read

Command write

Command write

Commandwrite

Command write

Command write

Command write

Command write

Command write

Commandwrite

Command write

Command write

Command write

Command write

Command write

Op-Code

on DQ Bus

TCO DS

FFFFH

TCO CT

0000H

TCO PA

nnnnH

SFF

TCO CT

0000H

TCO CT

8040H

TCO SC

3808H

SPS M@HM

Comments

Clear power-up anomalies.

Target Device Select register to disable local device selection.

Disable Device Select feature.

Target Control register for reset.

Causes Reset.

Target Page Address register to set page for cascaded operation.

Page Address value.

Set Full flag; allows access to next device (repeat previous

two cycles plus this one for each device in chain.

Target Control register for reset of Full flags, but not Page address.

Causes Reset.

Target Control register for initial values.

Control register value.

Target Segment Count Control register

Set both Segment counters to write to Segment 1, 2, and 3, and

read from Segment 0.

Set Data reads from Segment 0 of the Highest-Priority match.

1

2

2

2,3

1

1

4

4

4

Control bus

/E /CM /W /EC

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

H

L

L

L

L

L

L

L

L

L

L

L

L

L

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

Notes

Table 6: Example Initialization Routine

L

L

L

L

L

L

L

L

L

L

L

L

L

L

Notes:

1. Toggling the /RESET pin generates the same effect as this reset of the Control register, but good programming

practice dictates a software reset for initialization to account for all possible prior conditions.

2. This instruction may be omitted for a single LANCAM application.

3. The last SFF will cause the /FF pin in the last chip in a daisy chain to go LOW. In a daisy chain, DS needs to be set equal to PA

to read out a particular chip prior to a match condition.

4. A typical LANCAM control environment: Enable match flag; Enable full flag; 48 CAM bits, 16 RAM bits; Disable comparison

masking; and Enable address increment. See Table 8 on page 21 for Control Register bit assignments.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MU9C1902-35SC | x9 Asynchronous FIFO |

| MU9C1902-35PC | x9 Asynchronous FIFO |

| MU9C1902-35EC | x9 Asynchronous FIFO |

| MU9C1902-25SC | x9 Asynchronous FIFO |

| MU9C1902-25PC | x9 Asynchronous FIFO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MU9C1640-55DC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Content Addressable Memory |

| MU9C16K64M-50B568C | 制造商:MUSIC 制造商全稱:MUSIC Semiconductors 功能描述:MU9C RCP Family |

| MU9C16K64M-70B568C | 制造商:MUSIC 制造商全稱:MUSIC Semiconductors 功能描述:MU9C RCP Family |

| MU9C16K64M-90B568C | 制造商:MUSIC 制造商全稱:MUSIC Semiconductors 功能描述:MU9C RCP Family |

| MU9C1902-20EC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Asynchronous FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。