- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄68018 > MSP430A002IPMR (TEXAS INSTRUMENTS INC) 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | MSP430A002IPMR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP64 |

| 封裝: | GREEN, PLASTIC, LQFP-64 |

| 文件頁(yè)數(shù): | 31/62頁(yè) |

| 文件大小: | 1007K |

| 代理商: | MSP430A002IPMR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

MSP430x13x, MSP430x14x, MSP430x14x1

MIXED SIGNAL MICROCONTROLLER

SLAS272F JULY 2000 REVISED JUNE 2004

37

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature (unless otherwise

noted) (continued)

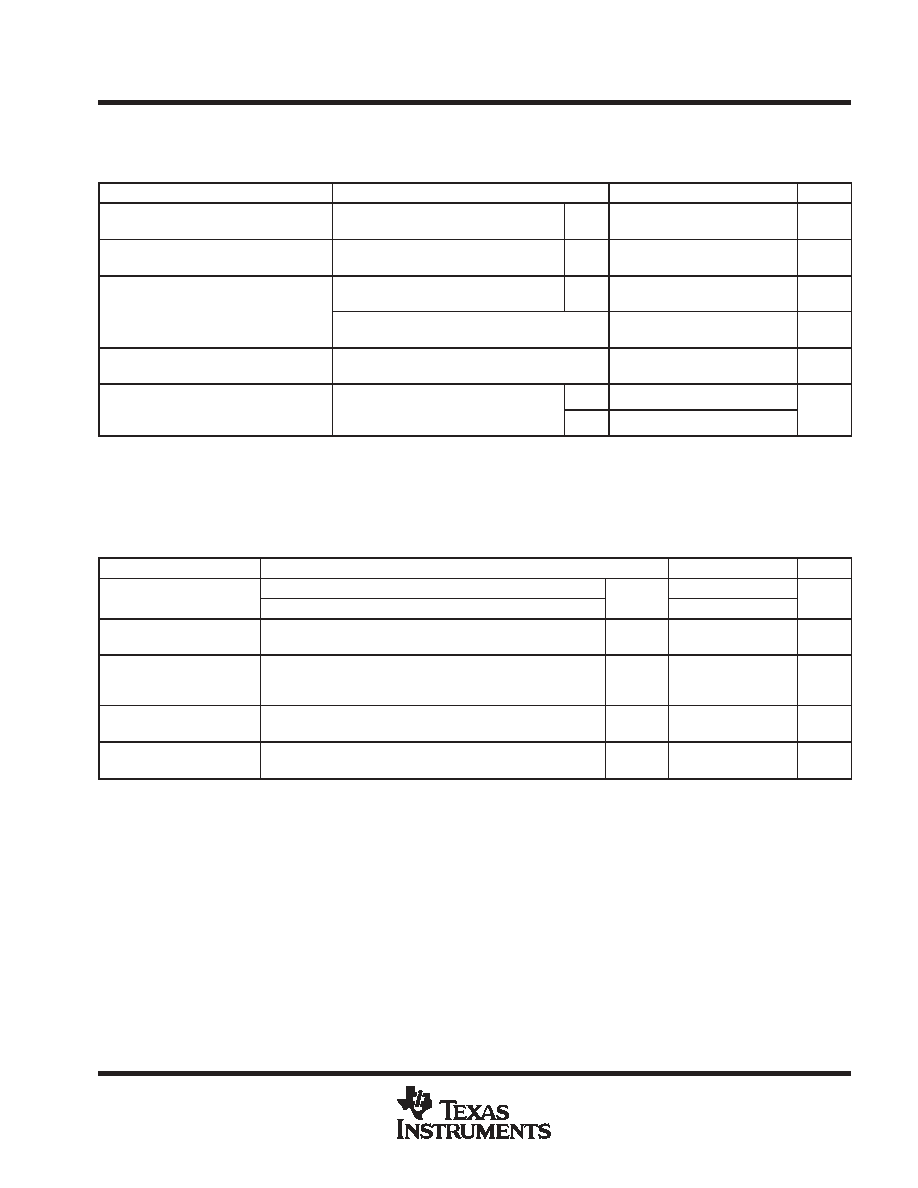

12-bit ADC, timing parameters

PARAMETER

TEST CONDITIONS

MIN

NOM

MAX

UNIT

fADC12CLK

For specified performance of ADC12

linearity parameters

2.2V/

3V

0.45

5

6.3

MHz

fADC12OSC

Internal ADC12

oscillator

ADC12DIV=0,

fADC12CLK=fADC12OSC

2.2 V/

3V

3.7

6.3

MHz

tCONVERT

Conversion time

CVREF+ ≥ 5 F, Internal oscillator,

fADC12OSC = 3.7 MHz to 6.3 MHz

2.2 V/

3 V

2.06

3.51

s

tCONVERT

Conversion time

External fADC12CLK from ACLK, MCLK or SMCLK:

ADC12SSEL

≠ 0

13

×ADC12DIV×

1/fADC12CLK

s

tADC12ON

Turn on settling time of

the ADC

(see Note 1)

100

ns

tSample

Sampling time

RS = 400 , RI = 1000 ,

CI = 30 pF

3 V

1220

ns

tSample

Sampling time

S

I

CI = 30 pF

τ = [RS + RI] x CI;(see Note 2)

2.2 V

1400

ns

Not production tested, limits characterized

Not production tested, limits verified by design

NOTES:

1. The condition is that the error in a conversion started after tADC12ON is less than ±0.5 LSB. The reference and input signal are already

settled.

2. Approximately ten Tau (

τ) are needed to get an error of less than ±0.5 LSB:

tSample = ln(2n+1) x (RS + RI) x CI+ 800 ns where n = ADC resolution = 12, RS = external source resistance.

12-bit ADC, linearity parameters

PARAMETER

TEST CONDITIONS

MIN

NOM

MAX

UNIT

EI

Integral linearity error

1.4 V

≤ (VeREF+ VREF/VeREF) min ≤ 1.6 V

2.2 V/3 V

±2

LSB

EI

Integral linearity error

1.6 V < (VeREF+ VREF/VeREF) min ≤ [V(AVCC)]

2.2 V/3 V

±1.7

LSB

ED

Differential linearity

error

(VeREF+ VREF/VeREF)min ≤ (VeREF+ VREF/VeREF),

CVREF+ = 10 F (tantalum) and 100 nF (ceramic)

2.2 V/3 V

±1

LSB

EO

Offset error

(VeREF+ VREF/VeREF)min ≤ (VeREF+ VREF/VeREF),

Internal impedance of source RS < 100 ,

CVREF+ = 10 F (tantalum) and 100 nF (ceramic)

2.2 V/3 V

±2

±4

LSB

EG

Gain error

(VeREF+ VREF/VeREF)min ≤ (VeREF+ VREF/VeREF),

CVREF+ = 10 F (tantalum) and 100 nF (ceramic)

2.2 V/3 V

±1.1

±2

LSB

ET

Total unadjusted

(VeREF+ VREF/VeREF)min ≤ (VeREF+ VREF/VeREF),

CVREF+ = 10 F (tantalum) and 100 nF (ceramic)

2.2 V/3 V

±2

±5

LSB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSP430A006IRTDR | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQCC64 |

| MSP430A006IPWR | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP64 |

| MSP430A007IRTDR | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQCC64 |

| MSP430A007IPMR | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP64 |

| MSP430A015IPMR | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSP430A003IPWR | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLER |

| MSP430A004IPW | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLER |

| MSP430A004IPWR | 制造商:Texas Instruments 功能描述: |

| MSP430A005IPW | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLER |

| MSP430A005IPWR | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:MIXED SIGNAL MICROCONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。