- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8144ETVT1000A (FREESCALE SEMICONDUCTOR INC) 133 MHz, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8144ETVT1000A |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 133 MHz, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCPBGA-783 |

| 文件頁數(shù): | 29/80頁 |

| 文件大小: | 1251K |

| 代理商: | MSC8144ETVT1000A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Electrical Characteristics

MSC8144E Quad Core Digital Signal Processor Data Sheet, Rev. 14

Freescale Semiconductor

35

The following sections include illustrations and tables of clock diagrams, signals, and parallel I/O outputs and inputs.

2.6.1

Start-Up Timing

Starting the device requires coordination among several input sequences including clocking, reset, and power. Section 2.6.2

describes the clocking characteristics. Section 2.6.3 describes the reset and power-up characteristics. You must use the

following guidelines when starting up an MSC8144E device:

PORESET and TRST must be asserted externally for the duration of the power-up sequence using the VDDIO (3.3 V)

supply. See Table 19 for timing. TRST must be deasserted before normal operation begins to ensure correct

initialization of the Security Engine.

Note:

For applications that use M3 memory, M3_RESET should replicate the PORESET sequence timing, but using the

CLKIN should start toggling at least 32 cycles before the PORESET deassertion to guarantee correct device operation

CLKIN and PCI_CLK_IN should either be stable low during the power-up of VDDIO supply and start their swings after

power-up or should swing within VDDIO range during VDDIO power-up., so their amplitude grows as VDDIO grows

during power-up.

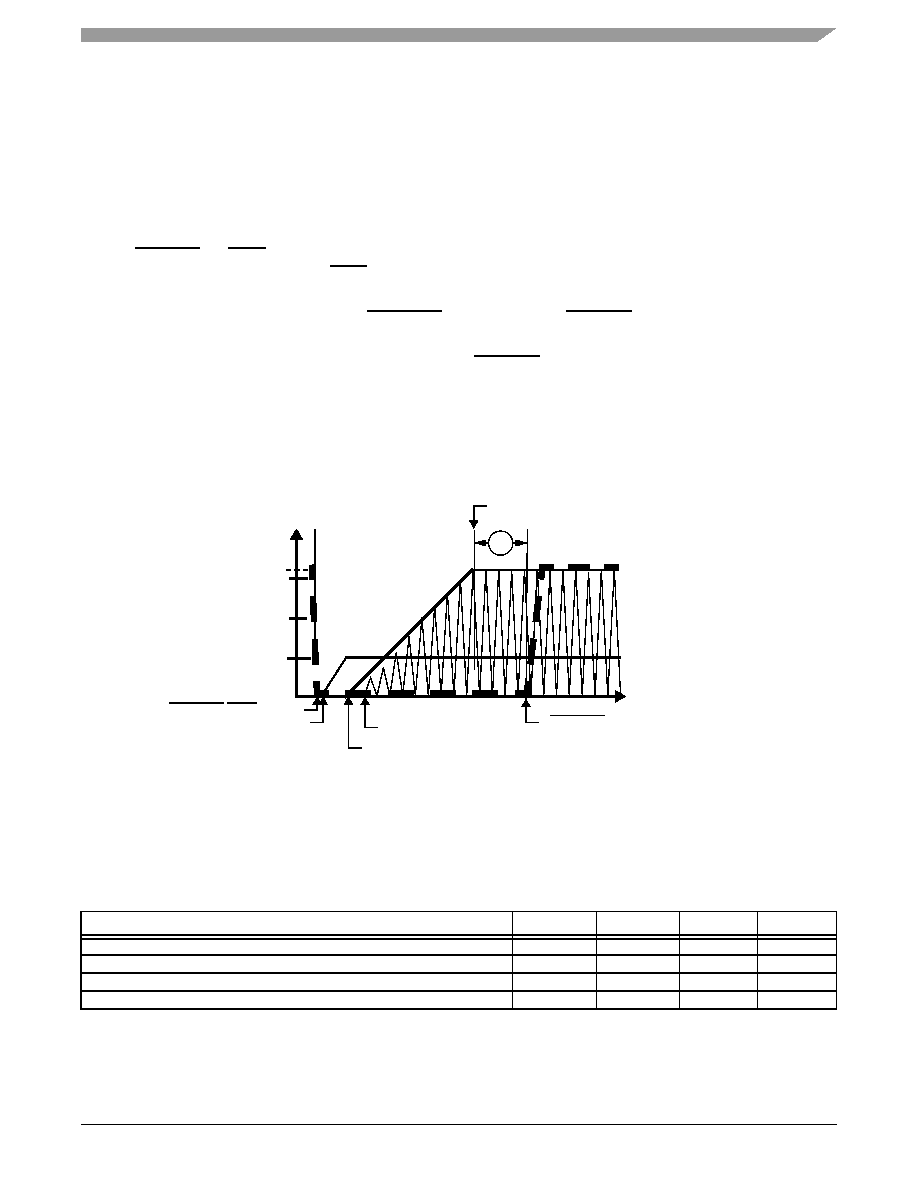

Figure 6 shows a sequence in which VDDIO is raised after VDD and CLKIN begins to toggle with the raise of VDDIO supply.

2.6.2

Clock and Timing Signals

The following sections include a description of clock signal characteristics. Table 16 shows the maximum frequency values for

CLKIN and PCI_CLK_IN. The user must ensure that maximum frequency values are not exceeded.

Figure 6. Start-Up Sequence with VDD Raised Before VDDIO with CLKIN Started with VDDIO

Table 16. Clock Frequencies

Characteristic

Symbol

Min

Max

Unit

CLKIN frequency

FCLKIN

33

133

MHz

PCI_CLK_IN frequency

FPCI_CLK_IN

33

133

MHz

CLKIN duty cycle

DCLKIN

40

60

%

PCI_CLK_IN duty cycle

DPCI_CLK_IN

40

60

%

Vo

lt

a

g

e

Time

3.3 V

VDDIO Nominal

PORESET/TRST asserted

VDD Nominal

CLKIN starts toggling

VDD applied

PORESET

1

VDDIO applied

1.0 V

VDDIO = Nominal

VDD = Nominal

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8144VT800B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144TVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144VT1000A | 133 MHz, OTHER DSP, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8144ETVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144ETVT800A | 制造商:Rochester Electronics LLC 功能描述: 制造商:Freescale Semiconductor 功能描述: |

| MSC8144ETVT800B | 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144EVT1000A | 制造商:Freescale Semiconductor 功能描述:DSP 32BIT 1GHZ 1000MIPS 783FCBGA - Trays |

| MSC8144EVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-Bit 1GHz 1000MIPS 783-Pin FCBGA Each 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA 制造商:Freescale 功能描述:DSP 32-Bit 1GHz 1000MIPS 783-Pin FCBGA Each |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。