- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25623 > MR80C52XXX-36SCD (ATMEL CORP) 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MR80C52XXX-36SCD |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| 封裝: | LCC-44 |

| 文件頁(yè)數(shù): | 26/109頁(yè) |

| 文件大小: | 10824K |

| 代理商: | MR80C52XXX-36SCD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)

271

7593L–AVR–09/12

AT90USB64/128

If the endpoint uses two banks, the second one can be read by the HOST while the current is

being written by the CPU. Then, when the CPU clears FIFOCON, the next bank may be already

ready (free) and TXINI is set immediately.

23.14.2.1

Abort

An “abort” stage can be produced by the host in some situations:

In a control transaction: ZLP data OUT received during a IN stage

In an isochronous IN transaction: ZLP data OUT received on the OUT endpoint during a IN

stage on the IN endpoint

...

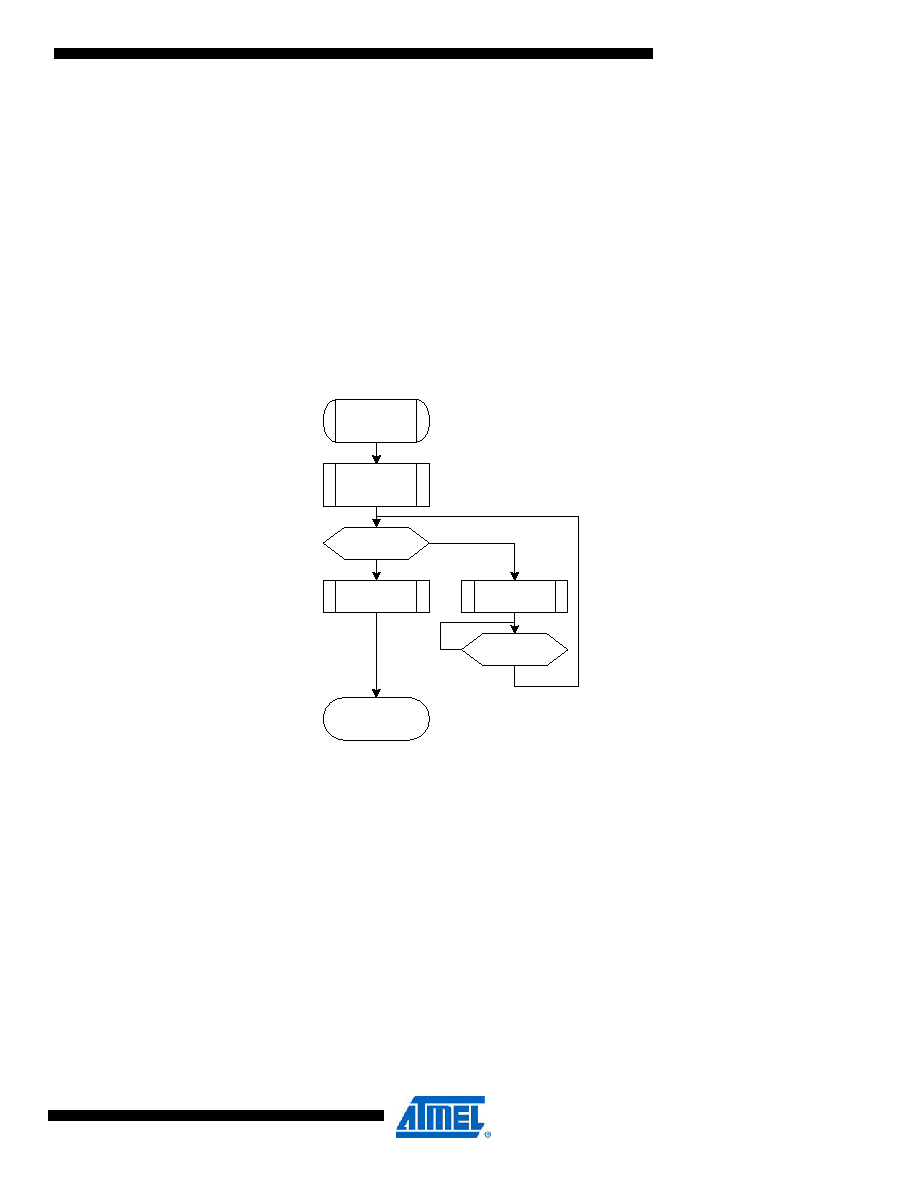

The KILLBK bit is used to kill the last “written” bank. The best way to manage this abort is to per-

form the following operations:

Table 23-1.

Abort flow.

23.15 Isochronous mode

23.15.1

An underflow can occur during IN stage if the host attempts to read a bank which is empty. In

this situation, the UNDERFI interrupt is triggered.

An underflow can also occur during OUT stage if the host send a packet while the banks are

already full. Typically, he CPU is not fast enough. The packet is lost.

It is not possible to have underflow error during OUT stage, in the CPU side, since the CPU

should read only if the bank is ready to give data (RXOUTI=1 or RWAL=1)

23.15.2

CRC error

A CRC error can occur during OUT stage if the USB controller detects a bad received packet. In

this situation, the STALLEDI interrupt is triggered. This does not prevent the RXOUTI interrupt

from being triggered.

Endpoint

Abort

Abort done

Abort is based on the fact

that no banks are busy,

meaning that nothing has to

be sent.

Disable the TXINI interrupt.

Endpoint

reset

NBUSYBK

=0

Yes

Clear

UEIENX.

TXINE

No

KILLBK=1

Yes

Kill the last written

bank.

Wait for the end of the

procedure.

No

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MD80C32-16SHXXX | 8-BIT, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR80C32E-20/883:RD | 8-BIT, 20 MHz, MICROCONTROLLER, CQCC44 |

| MR80C52XXX-30SCR | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C32-25/883:D | 8-BIT, 25 MHz, MICROCONTROLLER, CQFP44 |

| MD83C154XXX-36/883D | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MR80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 80C86 16BIT CMOS 8MHZ 44PLCC - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。