- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25638 > MR80C52EXXX-12:RD (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MR80C52EXXX-12:RD |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| 文件頁數(shù): | 7/46頁 |

| 文件大小: | 7004K |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

139

7593L–AVR–09/12

AT90USB64/128

Note:

1. The CTCn and PWMn1:0 bit definition names are obsolete. Use the WGMn2:0 definitions. However, the functionality and

location of these bits are compatible with previous versions of the timer.

15.10.3

TCCR1B – Timer/Counter1 Control Register B

15.10.4

TCCR3B – Timer/Counter3 Control Register B

Bit 7 – ICNCn: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the Noise Canceler is

activated, the input from the Input Capture Pin (ICPn) is filtered. The filter function requires four

successive equal valued samples of the ICPn pin for changing its output. The input capture is

therefore delayed by four Oscillator cycles when the noise canceler is enabled.

Bit 6 – ICESn: Input Capture Edge Select

This bit selects which edge on the Input Capture Pin (ICPn) that is used to trigger a capture

event. When the ICESn bit is written to zero, a falling (negative) edge is used as trigger, and

when the ICESn bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICESn setting, the counter value is copied into the

Input Capture Register (ICRn). The event will also set the Input Capture Flag (ICFn), and this

can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

When the ICRn is used as TOP value (see description of the WGMn3:0 bits located in the

TCCRnA and the TCCRnB Register), the ICPn is disconnected and consequently the input cap-

ture function is disabled.

Bit 5 – Reserved bit

This bit is reserved for future use. For ensuring compatibility with future devices, this bit must be

written to zero when TCCRnB is written.

Bit 4:3 – WGMn3:2: Waveform Generation mode

See TCCRnA Register description.

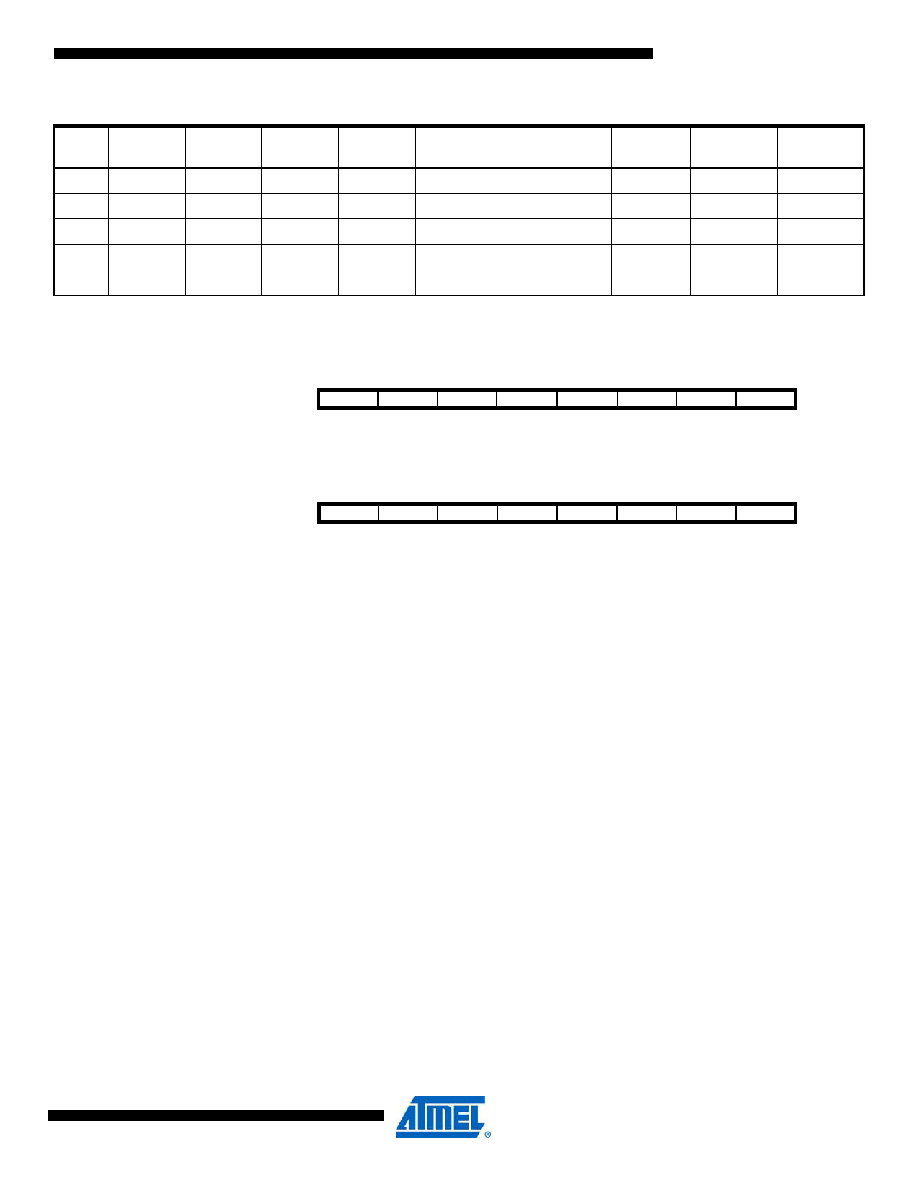

11

1

0

1

PWM, phase correct

OCRnA

TOP

BOTTOM

12

1

0

CTC

ICRn

Immediate

MAX

13

110

1

(Reserved)

–

14

1

0

Fast PWM

ICRn

TOP

15

1

Fast PWM

OCRnA

TOP

Table 15-4.

Waveform Generation mode bit description

(1). (Continued)

Mode

WGMn3

WGMn2

(CTCn)

WGMn1

(PWMn1)

WGMn0

(PWMn0)

Timer/Counter mode of

operation

TOP

Update of

OCRn

x at

TOVn flag

set on

Bit

7

65

4

3

21

0

ICNC1

ICES1

–

WGM13

WGM12

CS12

CS11

CS10

TCCR1B

Read/write

R/W

R

R/W

Initial value

0

Bit

7654

3

2

10

ICNC3

ICES3

–

WGM33

WGM32

CS32

CS31

CS30

TCCR3B

Read/write

R/W

R

R/W

Initial value

0000

0

00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MR80C32E-16P883R | 8-BIT, 16 MHz, MICROCONTROLLER, CQCC44 |

| MD80C52EXXX-30 | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CDIP40 |

| MR83C154DCXXX-12/883R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C154-36P883R | 8-BIT, 36 MHz, MICROCONTROLLER, CQFP44 |

| MD80C52EXXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MR80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 80C86 16BIT CMOS 8MHZ 44PLCC - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。