- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25642 > MQ80C52EXXX-20P883R (ATMEL CORP) 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MQ80C52EXXX-20P883R |

| 廠(chǎng)商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| 封裝: | CERAMIC, QFP-44 |

| 文件頁(yè)數(shù): | 17/91頁(yè) |

| 文件大?。?/td> | 19688K |

| 代理商: | MQ80C52EXXX-20P883R |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)

29

7707F–AVR–11/10

AT90USB82/162

6.2.5

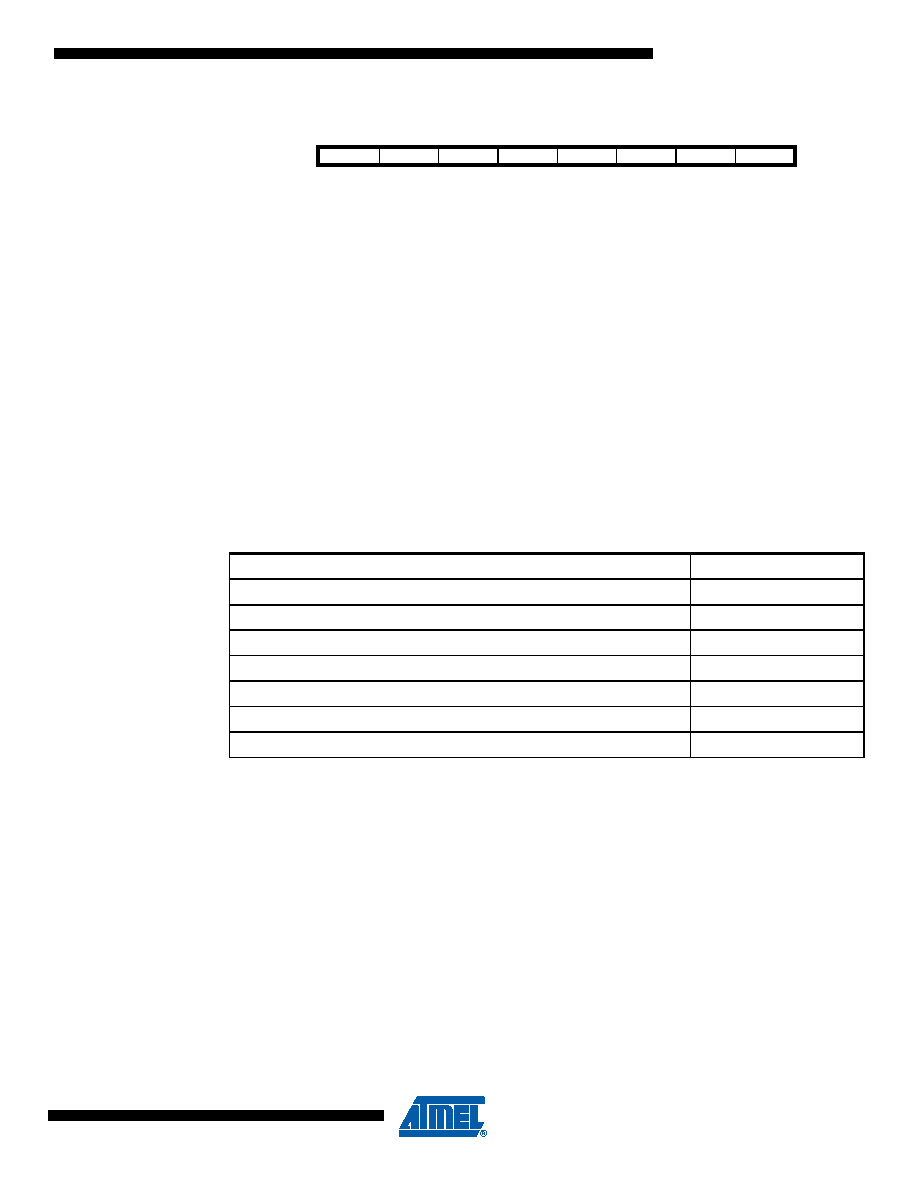

Clock Status Register – CLKSTA

Bit 7-2 - Reserved bits

These bits are reserved and will always read as zero.

Bit 1 – RCON: RC Oscillator On

This bit is set by hardware to one if the RC Oscillator is running.

This bit is set by hardware to zero if the RC Oscillator is stoped.

Bit 0 – EXTON: External Oscillator / Low Power Oscillator On

This bit is set by hardware to one if the External Oscillator / Low Power Oscillator is running.

This bit is set by hardware to zero if the External Oscillator / Low Power Oscillator is stoped.

6.3

Clock Sources

The device has the following clock source options, selectable by Flash Fuse bits as shown

below. The clock from the selected source is input to the AVR clock generator, and routed to the

appropriate modules.

Note:

1. For all fuses “1” means unprogrammed while “0” means programmed.

6.3.1

Default Clock Source

The device is shipped with low power crystal oscillator and with the fuse CKDIV8 programmed.

The startup time is set to maximum and time-out period enabled. (CKSEL = "1110", SUT = "01",

CKDIV8 = "0").

6.3.2

Clock Startup Sequence

Any clock source needs a sufficient V

CC to start oscillating and a minimum number of oscillating

cycles before it can be considered stable.

To ensure sufficient V

CC, the device issues an internal reset with a time-out delay (tTOUT) after

the device reset is released by all other reset sources. “On-chip Debug System” on page 45

describes the start conditions for the internal reset. The delay (t

TOUT) is timed from the Watchdog

Oscillator and the number of cycles in the delay is set by the SUTx and CKSELx fuse bits. The

selectable delays are shown in Table 6-2. The frequency of the Watchdog Oscillator is voltage

Bit

7

6

543

2

1

0

-

RCON

EXTON

CLKSTA

Read/Write

R

Initial Value

0

See Bit Description

Table 6-1.

Device Clocking Options Select

Device Clocking Option

CKSEL3..0

Low Power Crystal Oscillator

1111 - 1000

Reserved

0111 - 0110

Reserved

0101 - 0100

Reserved

0011

Calibrated Internal RC Oscillator

0010

External Clock

0000

Reserved

0001

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C32E-25SCR | 8-BIT, 25 MHz, MICROCONTROLLER, CQFP44 |

| MR80C52EXXX-36/883:RD | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| MR80C52TXXX-20SHXXX:R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQCC44 |

| MR80C52XXX-36/883:RD | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| MD83C154TXXX-20P883 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MQ82370-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ8238020 | 制造商:Intel 功能描述:CONTROLLER: OTHER |

| MQ82380-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ82380-20/R | 制造商:Rochester Electronics LLC 功能描述: |

| MQ82592 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。