- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25631 > MPC8548EVTAVJA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1500 MHz, MICROPROCESSOR, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MPC8548EVTAVJA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 1500 MHz, MICROPROCESSOR, PBGA783 |

| 封裝: | 29 X 29 MM, 1 MM PITCH, FLIP CHIP, LEAD FREE, PLASTIC, BGA-783 |

| 文件頁數(shù): | 92/142頁 |

| 文件大小: | 1504K |

| 代理商: | MPC8548EVTAVJA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁當前第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

Freescale Semiconductor

53

JTAG

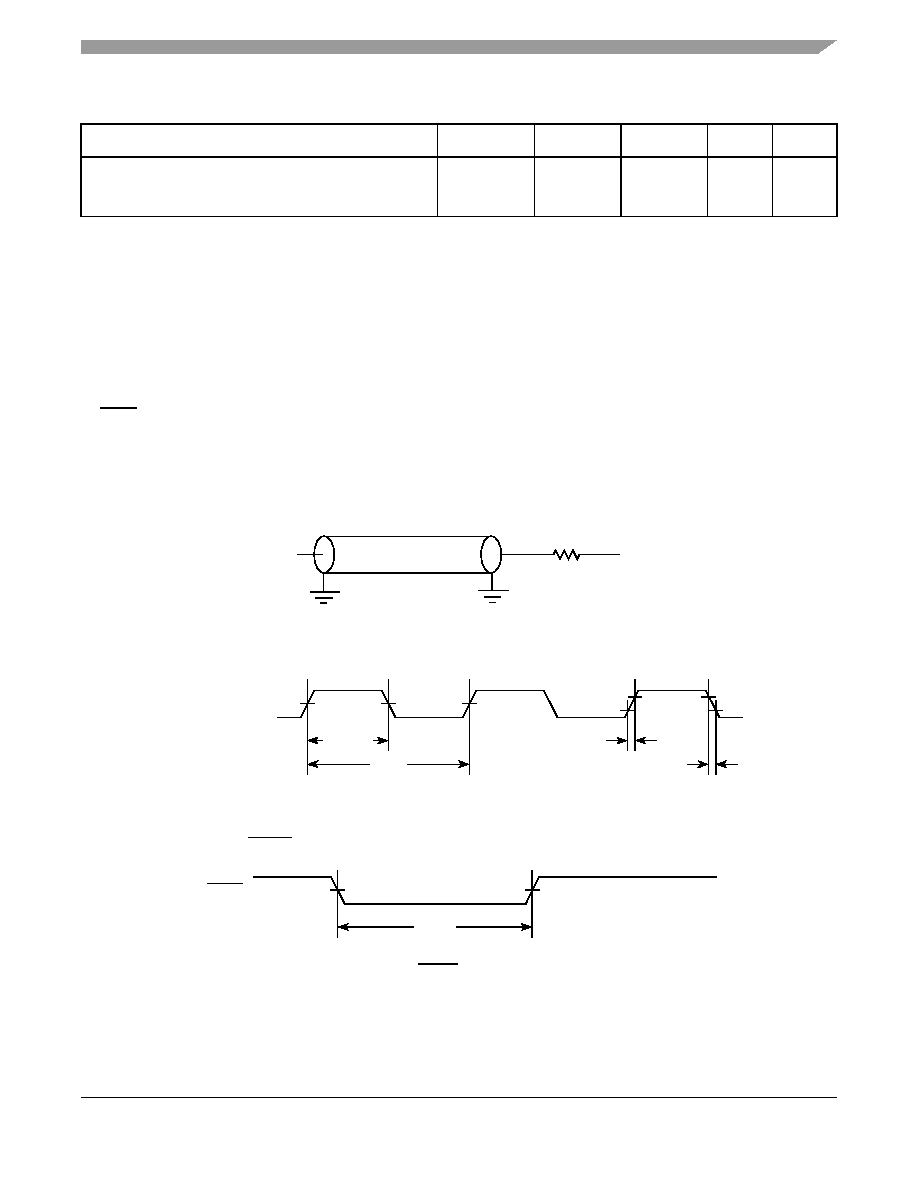

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

Figure 31 provides the TRST timing diagram.

Figure 31. TRST Timing Diagram

JTAG external clock to output high impedance:

Boundary-scan data

TDO

tJTKLDZ

tJTKLOZ

3

19

9

ns

5, 6

Notes:

1. All outputs are measured from the midpoint voltage of the falling/rising edge of tTCLK to the midpoint of the signal in question.

The output timings are measured at the pins. All output timings assume a purely resistive 50-

Ω load (see Figure 29).

Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tJTDVKH symbolizes JTAG device

timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the tJTG clock reference (K)

going to the high (H) state or setup time. Also, tJTDXKH symbolizes JTAG timing (JT) with respect to the time data input signals

(D) went invalid (X) relative to the tJTG clock reference (K) going to the high (H) state. Note that, in general, the clock reference

symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the

latter convention is used with the appropriate letter: R (rise) or F (fall).

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

4. Non-JTAG signal input timing with respect to tTCLK.

5. Non-JTAG signal output timing with respect to tTCLK.

6. Guaranteed by design.

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)1 (continued)

Parameter

Symbol2

Min

Max

Unit

Notes

Output

Z0 = 50 Ω

OVDD/2

RL = 50 Ω

JTAG

tJTKHKL

tJTGR

External Clock

VM

tJTG

tJTGF

VM = Midpoint Voltage (OVDD/2)

TRST

VM = Midpoint Voltage (OVDD/2)

VM

tTRST

相關PDF資料 |

PDF描述 |

|---|---|

| MPC8548VTAQH | 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 |

| MPC8548ECVUAUJB | 32-BIT, 1333 MHz, MICROPROCESSOR, CBGA783 |

| MPC8547EVTAUJA | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA783 |

| MPC8543CVUANGA | 32-BIT, 800 MHz, MICROPROCESSOR, CBGA783 |

| MPC8545CHXANG | 32-BIT, 800 MHz, MICROPROCESSOR, CBGA783 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8548EVUAQG | 功能描述:微處理器 - MPU PQ38 8548E PBFREE RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8548EVUATG | 功能描述:微處理器 - MPU PQ38 8548E PB-FREE RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8548EVUAUJ | 功能描述:微處理器 - MPU PQ38 8548E PBFREE RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8548EVUAVH | 制造商:Freescale Semiconductor 功能描述:PQ38 8548E PB-FREE - Bulk |

| MPC8548EVUAVK | 制造商:Freescale Semiconductor 功能描述:PQ38 8548E PB-FREE - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。