- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371135 > MPC850EC (Motorola, Inc.) Communications Controller Hardware Specifications PDF資料下載

參數(shù)資料

| 型號(hào): | MPC850EC |

| 廠商: | Motorola, Inc. |

| 英文描述: | Communications Controller Hardware Specifications |

| 中文描述: | 通信控制器的硬件規(guī)格 |

| 文件頁數(shù): | 15/68頁 |

| 文件大?。?/td> | 384K |

| 代理商: | MPC850EC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

MOTOROLA

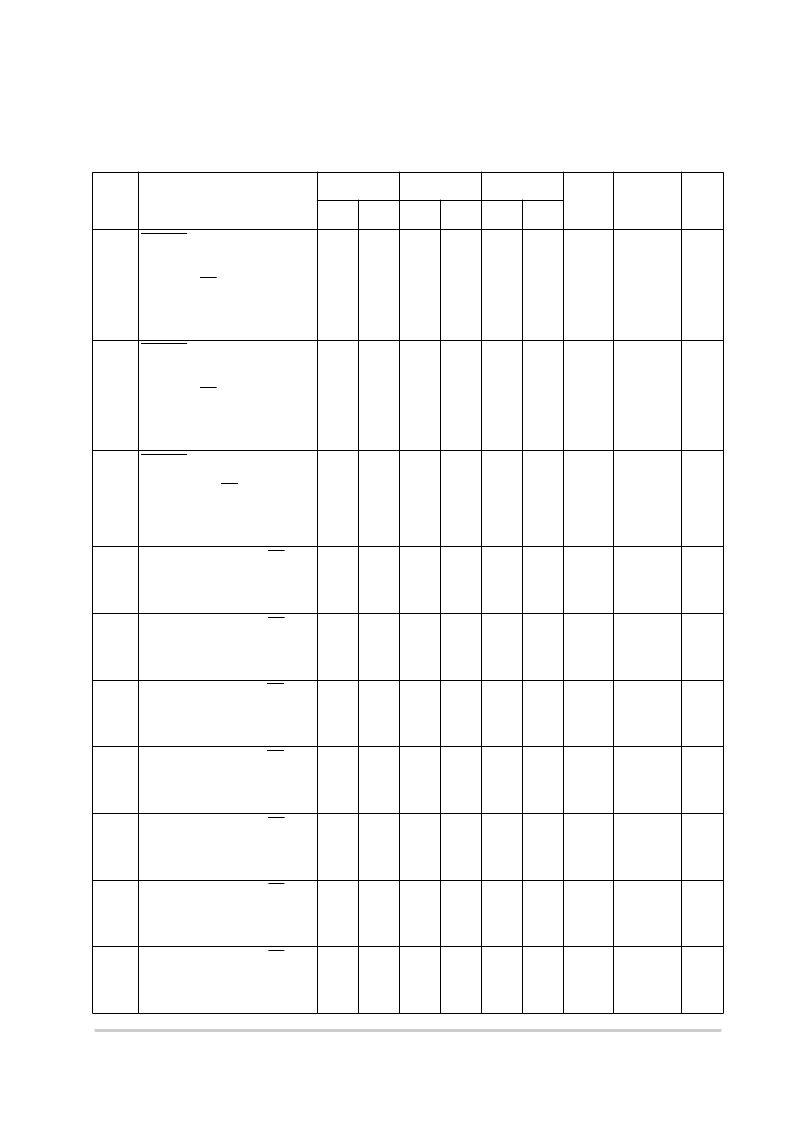

MPC850 (Rev. A/B/C) Hardware Specifications

15

Layout Practices

B30b

WE[0–3] negated to A[6–31]

invalid

GPCM write access, TRLX = 1,

CSNT = 1. CS negated to

A[6–31] Invalid GPCM write

access TRLX = 1, CSNT = 1,

ACS = 10 or ACS = 11, EBDF = 0

28.00

—

43.00

—

36.00

—

1.500

50.00

ns

B30c

WE[0–3] negated to A[6–31]

invalid

GPCM write access, TRLX = 0,

CSNT = 1. CS negated to

A[6–31] invalid GPCM write

access, TRLX = 0, CSNT = 1,

ACS = 10 or ACS = 11, EBDF = 1

5.00

—

8.00

—

6.00

—

0.375

50.00

ns

B30d

WE[0–3] negated to A[6–31]

invalid GPCM write access TRLX

= 1, CSNT =1, CS negated to

A[6–31] invalid GPCM write

access TRLX = 1, CSNT = 1,

ACS = 10 or ACS = 11, EBDF = 1

25.00

—

39.00

—

31.00

—

1.375

50.00

ns

B31

CLKOUT falling edge to CS valid

- as requested by control bit

CST4 in the corresponding word

in the UPM

1.50

6.00

1.50

6.00

1.50

6.00

—

50.00

ns

B31a

CLKOUT falling edge to CS valid

- as requested by control bit

CST1 in the corresponding word

in the UPM

5.00

12.00

8.00

14.00

6.00

13.00

0.250

50.00

ns

B31b

CLKOUT rising edge to CS valid

- as requested by control bit

CST2 in the corresponding word

in the UPM

1.50

8.00

1.50

8.00

1.50

8.00

—

50.00

ns

B31c

CLKOUT rising edge to CS valid

- as requested by control bit

CST3 in the corresponding word

in the UPM

5.00

12.00

8.00

14.00

6.00

13.00

0.250

50.00

ns

B31d

CLKOUT falling edge to CS valid

- as requested by control bit

CST1 in the corresponding word

in the UPM EBDF = 1

9.00

14.00

13.00

18.00

11.00

16.00

0.375

50.00

ns

B32

CLKOUT falling edge to BS valid

- as requested by control bit

BST4 in the corresponding word

in the UPM

1.50

6.00

1.50

6.00

1.50

6.00

—

50.00

ns

B32a

CLKOUT falling edge to BS valid

- as requested by control bit

BST1 in the corresponding word

in the UPM, EBDF = 0

5.00

12.00

8.00

14.00

6.00

13.00

0.250

50.00

ns

Table 6. Bus Operation Timing

1

(continued)

Num

Characteristic

50 MHz

66 MHz

80 MHz

FFACT

Cap Load

(default

50 pF)

Unit

Min

Max

Min

Max

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC850ED | Communications Controller Hardware Specifications |

| MPC850SAR | Communications Controller Hardware Specifications |

| MPC859P | PowerQUICC⑩ Family Technical Summary |

| MPC859TTS | PowerQUICC⑩ Family Technical Summary |

| MPC859TTSD | PowerQUICC⑩ Family Technical Summary |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC850SRCVR50BU | 功能描述:微處理器 - MPU POWER QUICC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC850SRCVR66BU | 功能描述:微處理器 - MPU POWER QUICC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC850SRCZQ50BU | 功能描述:微處理器 - MPU POWERPC MPU W/CPM RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC850SRCZQ66BU | 功能描述:微處理器 - MPU POWERPC MPU W/CPM RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC850SRVR50BU | 功能描述:微處理器 - MPU POWER QUICC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。