- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄201872 > MPC8347ECVRALD (FREESCALE SEMICONDUCTOR INC) 32-BIT, 667 MHz, RISC PROCESSOR, PBGA620 PDF資料下載

參數(shù)資料

| 型號: | MPC8347ECVRALD |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 667 MHz, RISC PROCESSOR, PBGA620 |

| 封裝: | 29 X 29 MM, 2.46 MM HEIGHT, 1 MM PITCH, LEAD FREE, PLASTIC, BGA-620 |

| 文件頁數(shù): | 78/102頁 |

| 文件大?。?/td> | 1094K |

| 代理商: | MPC8347ECVRALD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁當(dāng)前第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

MPC8347E PowerQUICC II Pro Integrated Host Processor Hardware Specifications, Rev. 11

Freescale Semiconductor

77

Clocking

As shown in Figure 41, the primary clock input (frequency) is multiplied up by the system phase-locked

loop (PLL) and the clock unit to create the coherent system bus clock (csb_clk), the internal clock for the

DDR controller (ddr_clk), and the internal clock for the local bus interface unit (lbiu_clk).

The csb_clk frequency is derived from a complex set of factors that can be simplified into the following

equation:

csb_clk = {PCI_SYNC_IN × (1 + CFG_CLKIN_DIV)} × SPMF

In PCI host mode, PCI_SYNC_IN × (1 + CFG_CLKIN_DIV) is the CLKIN frequency.

The csb_clk serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies the

csb_clk frequency to create the internal clock for the e300 core (core_clk). The system and core PLL

multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL),

which is loaded at power-on reset or by one of the hard-coded reset options. See the chapter on reset,

clocking, and initialization in the MPC8349E Reference Manual for more information on the clock

subsystem.

The internal ddr_clk frequency is determined by the following equation:

ddr_clk = csb_clk × (1 + RCWL[DDRCM])

ddr_clk is not the external memory bus frequency; ddr_clk passes through the DDR clock divider (

÷2) to

create the differential DDR memory bus clock outputs (MCK and MCK). However, the data rate is the

same frequency as ddr_clk.

The internal lbiu_clk frequency is determined by the following equation:

lbiu_clk = csb_clk × (1 + RCWL[LBIUCM])

lbiu_clk is not the external local bus frequency; lbiu_clk passes through the LBIU clock divider to create

the external local bus clock outputs (LSYNC_OUT and LCLK[0:2]). The LBIU clock divider ratio is

controlled by LCCR[CLKDIV].

In addition, some of the internal units may have to be shut off or operate at lower frequency than the

csb_clk frequency. Those units have a default clock ratio that can be configured by a memory-mapped

register after the device exits reset. Table 53 specifies which units have a configurable clock frequency.

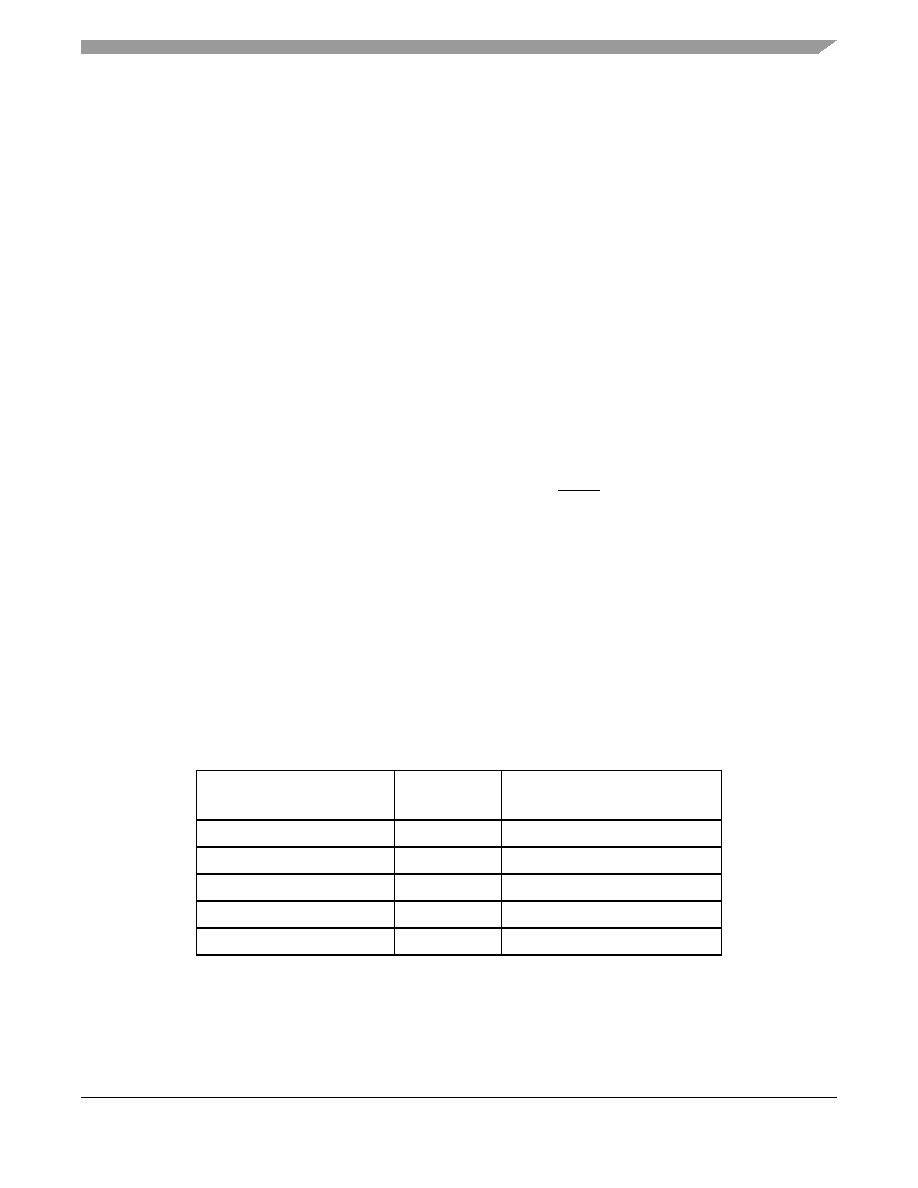

Table 53. Configurable Clock Units

Unit

Default

Frequency

Options

TSEC1

csb_clk/3

Off,

csb_clk, csb_clk/2, csb_clk/3

TSEC2, I2C1

csb_clk/3

Off,

csb_clk, csb_clk/2, csb_clk/3

Security core

csb_clk/3

Off,

csb_clk, csb_clk/2, csb_clk/3

USB DR, USB MPH

csb_clk/3

Off, csb_clk, csb_clk/2,

csb_clk/3

PCI and DMA complex

csb_clk

Off,

csb_clk

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8347ECZQAGF | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA620 |

| MCF51QH64VHS | FLASH, 50 MHz, MICROCONTROLLER, QCC44 |

| MB95F563HPFT-G-JNE2 | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PDSO20 |

| MB95F563HWQN-G-JNERE1 | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQCC32 |

| MB95F563KPFT-G-JNE2 | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8347ECVRALDB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECVRALFB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECVVADDB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECVVADFB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8347EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications |

| MPC8347ECVVAGDB | 功能描述:微處理器 - MPU 8349 TBGA NO PB W/ ENC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。