- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377969 > ML2003CQ (FAIRCHILD SEMICONDUCTOR CORP) Logarithmic Gain/Attenuator PDF資料下載

參數(shù)資料

| 型號: | ML2003CQ |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 運動控制電子 |

| 英文描述: | Logarithmic Gain/Attenuator |

| 中文描述: | LOG OR ANTILOG AMPLIFIER, 0.0199 MHz BAND WIDTH, PQCC20 |

| 封裝: | PLASTIC, CC-20 |

| 文件頁數(shù): | 8/11頁 |

| 文件大?。?/td> | 88K |

| 代理商: | ML2003CQ |

ML2003, ML2004

PRODUCT SPECIFICATION

8

REV. 1.1.1 3/19/01

Table 2. Coarse Gain Settings (F3-F0 = 0)

The device also has the capability to read out the data word

stored in the latch. This can be done by parallel loading the

data from the latch back into the shift register when the latch

signal, LATO, is high. The LATO pulse must occur when

SCK is low. Then, the data word can be shifted out of the

shift register serially to the output, SOD, on falling edges of

the shift clock, SCK.

The loading and reading of the data word can be done

continuously or in burst. Since the shift register and latch

circuitry inside the device is static, there are no minimum

frequency requirements on the clocks or data pulses.

However, there is coupling (typically less than 100μV) of

the digital signals into the analog section. This coupling

can be minimized by clocking the data bursts in during

noncritical intervals or at a frequency outside the analog

frequency range.

Parallel Mode

The parallel mode is selected by setting SER/PAR pin low.

The parallel interface allows the gain settings to be set with

external switches or from a parallel microprocessor inter-

face.

In parallel mode, the shift register and latch are bypassed and

connections are made directly to the gain select bits with

external pins ATTEN/GAIN, C3-C0, and F3-F0. Tables 1

and 2 describe how these pins program the gain. The pins

ATTEN/GAIN, C3-C0, and F3-F0 have internal pulldown

resistors to GND. The typical value of these pulldown

resistors is 100k

.

C3 C2 C1 C0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

Ideal Gain (dB)

ATTEN/GAIN = 1 ATTEN/GAIN = 0

0

-1.5

-3.0

-4.5

-6.0

-7.5

-9.0

-10.5

-12.0

-13.5

-15.0

-16.5

-18.0

-19.5

-21.0

-22.5

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1.5

3.0

4.5

6.0

7.5

9.0

10.5

12.0

13.5

15.0

16.5

18.0

19.5

21.0

22.5

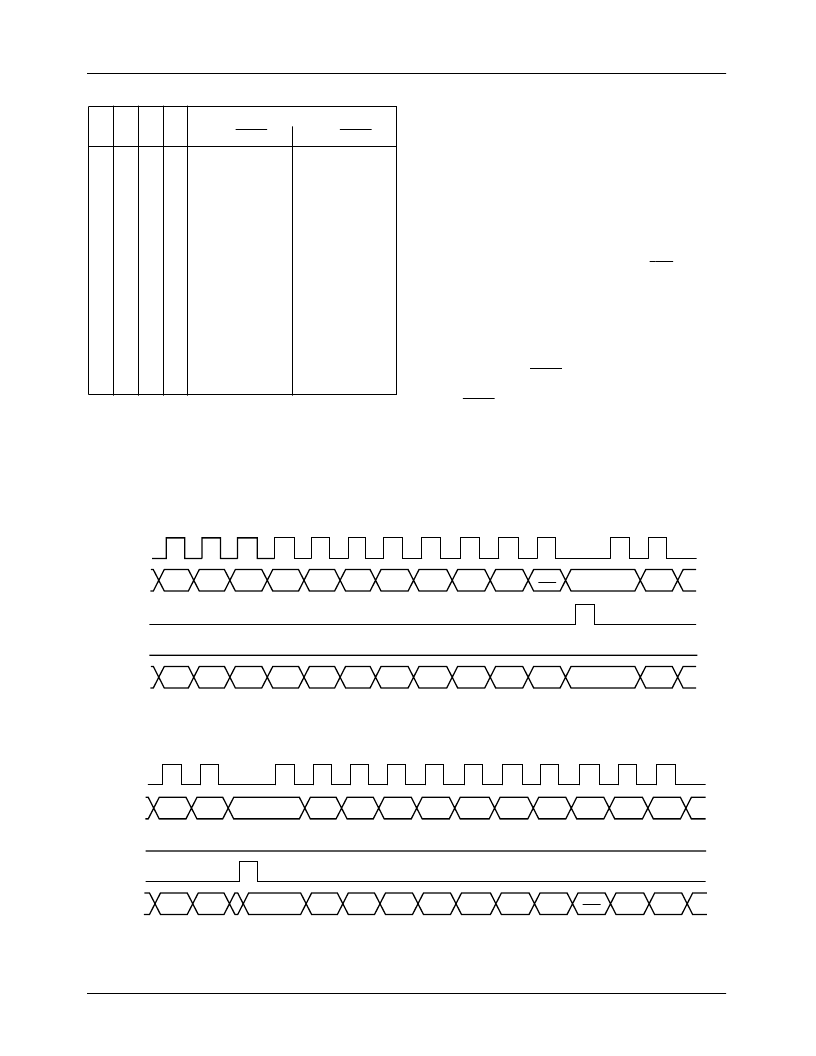

Figure 10. Serial Mode Timing

SCK

SCK

0

1

2

3

4

5

6

7

8

0

1

2

3

4

5

6

7

8

a) LOAD

b) READ

SID

SID

LATI

LATI

LATO

LATO

SOD

SOD

F0

F1

F2

F3

C0

C1

C2

C3

ATT/

GAIN

F0

F1

F2

F3

C0

C1

C2

C3

ATT/

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML2004 | Logarithmic Gain/Attenuator |

| ML2004CP | Logarithmic Gain/Attenuator |

| ML2004IP | Logarithmic Gain/Attenuator |

| ML2003 | Logarithmic Gain/Attenuaor With Serial and Parallel Interface(串/并行接口的對數(shù)增益衰減器) |

| ML2008 | μP Compatible Logarithmic Gain/Attenuator(微處理器兼容的對數(shù)增益衰減器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML2003CQX | 功能描述:線性穩(wěn)壓器 - 標(biāo)準(zhǔn) Gain/attenuator Logarithmic RoHS:否 制造商:STMicroelectronics 輸出類型: 極性: 輸出電壓:1.8 V 輸出電流:150 mA 負(fù)載調(diào)節(jié): 最大輸入電壓:5.5 V 線路調(diào)整率: 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOT-323-5L |

| ML2003IP | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:Logarithmic Gain/Attenuator |

| ML2003IQ | 功能描述:線性穩(wěn)壓器 - 標(biāo)準(zhǔn) Gain/attenuator Logarithmic RoHS:否 制造商:STMicroelectronics 輸出類型: 極性: 輸出電壓:1.8 V 輸出電流:150 mA 負(fù)載調(diào)節(jié): 最大輸入電壓:5.5 V 線路調(diào)整率: 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOT-323-5L |

| ML2003IQX | 功能描述:線性穩(wěn)壓器 - 標(biāo)準(zhǔn) Gain/attenuator Logarithmic RoHS:否 制造商:STMicroelectronics 輸出類型: 極性: 輸出電壓:1.8 V 輸出電流:150 mA 負(fù)載調(diào)節(jié): 最大輸入電壓:5.5 V 線路調(diào)整率: 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOT-323-5L |

| ML2004 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Logarithmic Gain/Attenuator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。